# **Product Specifications**

| Customer    |                   |

|-------------|-------------------|

| Model Name  | TFT029B101A       |

| Description | 320(RGB)x120 Dots |

| Description | 2.9" TFT LCD      |

| Date        | 2017/3/17         |

| Revision    | 1.0               |

|      | Customer Approval |  |  |  |  |  |

|------|-------------------|--|--|--|--|--|

|      |                   |  |  |  |  |  |

| Date |                   |  |  |  |  |  |

|      |                   |  |  |  |  |  |

| Engineering              |           |          |           |  |  |  |

|--------------------------|-----------|----------|-----------|--|--|--|

| Check Date Prepared Date |           |          |           |  |  |  |

| Sam huang                | 2017/3/17 | Jack guo | 2017/3/17 |  |  |  |

## **Table of Contents**

| 1 Record of Revision                  | 3  |

|---------------------------------------|----|

| 2 General Specifications              | 4  |

| 3 Input/Output Terminals              |    |

| 4 Absolute Maximum Ratings            |    |

| 5 Electrical Characteristics          | 7  |

| 6 Interface Timing                    | 9  |

| 7 Optical Characteristics             | 18 |

| 8 Environmental / Reliability Tests   |    |

| 9 Mechanical Drawing                  | 23 |

| 10 Packing                            | 24 |

| 11 Precautions For Use of LCD modules | 25 |

# 1 Record of Revision

| Rev | Issued Date | Description    | Editor   |

|-----|-------------|----------------|----------|

| 1.0 | 2017/3/17   | First Release. | Jack Guo |

|     |             |                |          |

|     |             |                |          |

|     |             |                |          |

|     |             |                |          |

|     |             |                |          |

|     |             |                |          |

|     |             |                |          |

|     |             |                |          |

|     |             |                |          |

|     |             |                |          |

|     |             |                |          |

|     |             |                |          |

|     |             |                |          |

# 2 General Specifications

|                 | Feature                        | Spec                          |  |  |

|-----------------|--------------------------------|-------------------------------|--|--|

|                 | Size                           | 2.9inch                       |  |  |

|                 | Resolution                     | 320(horizontal)*120(Vertical) |  |  |

|                 | Interface                      | RGB 18bit                     |  |  |

|                 | Connect type                   | Connector                     |  |  |

|                 | Color Depth                    | 262k                          |  |  |

| Characteristics | Technology type                | a-Si                          |  |  |

| Characteristics | Display Spec. Pixel pitch (mm) | 0.2205 x 0.2205               |  |  |

|                 | Pixel Configuration            | R.G.B. Vertical Stripe        |  |  |

|                 | Display Mode                   | Normally White                |  |  |

|                 | Driver IC                      | SSD2116Z                      |  |  |

|                 | Surface Treatment              | HC                            |  |  |

|                 | Viewing Direction              | 12 O'clock                    |  |  |

|                 | LCM (W x H x D) (mm)           | 76.90*38.22*3.26              |  |  |

|                 | Active Area(mm)                | 70.56 x 26.46                 |  |  |

| Mechanical      | With /Without TSP              | Without TSP                   |  |  |

|                 | Weight (g)                     | TBD                           |  |  |

|                 | LED Numbers                    | 6 LEDs                        |  |  |

Note 1: RoHS

Note 2: LCM weight tolerance: +/- 5%

# 3 Input/Output Terminals

| No.   | Symbol | Description                            |

|-------|--------|----------------------------------------|

| 1,2   | VBL-   | Backlight LED Cathode                  |

| 3,4   | VBL+   | Backlight LED Anode.                   |

| 5     | Y1(YU) | Touch panel up side                    |

| 6     | X1(XR) | Touch panel right side                 |

| 7     | NC     | NC NC                                  |

| 8     | RESET  | Reset Signal pin                       |

| 9     | CS     | Chip select                            |

| 10    | SCL    | Serial Clock.                          |

| 11    | SDA    | Serial Data Input                      |

| 12    | SDO    | Serial Data output                     |

| 13    | NC     | NC                                     |

| 14~19 | B0~B5  | Data bus                               |

| 20,21 | NC     | NC                                     |

| 22~27 | G0~G5  | Data bus                               |

| 28,29 | NC     | NC                                     |

| 30~35 | R0~R5  | Data bus                               |

| 36    | HSYNC  | Line Synchronous Signal                |

| 37    | VSYNC  | Frame Synchronous Signal               |

| 38    | DOTCLK | Dot-clock signal and oscillator source |

| 39    | GND    | Ground                                 |

| 40    | IOVCC  | Voltage input pin for logic            |

| 41    | VDD    | Booster input voltage pin              |

| 42    | VDD    | Booster input voltage pin              |

| 43    | Y2(YD) | Touch panel down side                  |

| 44    | X2(XL) | Touch panel Left side                  |

| 45-51 | NC     | NC                                     |

| 52    | DEN    | Display enable pin for controller      |

| 53    | GND    | Ground                                 |

| 54    | GND    | Ground                                 |

## 4 Absolute Maximum Ratings

## **Driving TFT LCD Panel**

| Item                           | Symbol            | Conditions | Rated value                   | Unit | Remarks   |

|--------------------------------|-------------------|------------|-------------------------------|------|-----------|

| Input voltage                  | VI                | Ta = 25°C  | -0.3 ~ V <sub>DDIO</sub> +0.3 | ٧    | Note 2    |

| Logic I/O power supply voltage | V <sub>DDIO</sub> | Ta = 25°C  | -0.3 ~ +4.0                   | V    |           |

| Analog power supply voltage    | V <sub>CI</sub>   | Ta = 25°C  | AGND-0.3 ~ +5.0               | ٧    |           |

| Temperature for storage        | Tstg              |            | -30 ~ +80                     | °C   | Note 3    |

| Temperature for operation      | Topr              | -          | -20 ~ +70                     | °C   | Note 3, 4 |

| LED input electric current     | I <sub>LED</sub>  | Ta = 25°C  | 70                            | mA   | Note 5    |

| LED electricity consumption    | P <sub>LED</sub>  | Ta = 25°C  | 238                           | mW   | Note 5    |

- Note 2) REST, CSB, SDI, SCK, DEN, B7~B0, G7~G0, R7~R0, VSYNC, HSYNC, DOTCLK

- Note 3) Humidity: 95%RH Max. (Ta = 40°C)

Maximum bulb temperature under 39°C (Ta>40°C) See to it that no dew will be condensed.

- Note 4) Panel surface temperature prescribes.

- Note 5) Power consumption of one LED (Ta = 25°C) (use 6 pieces LED)

## 5 Electrical Characteristics

## 5.1 Driving TFT LCD Panel

Ta = 25°C

|               |            |                      |                       |      |                       |       | 1a = 25 |

|---------------|------------|----------------------|-----------------------|------|-----------------------|-------|---------|

| Item          |            | Symbol               | Min.                  | Тур. | Max.                  | Unit  | Remarks |

| Logic I/O     | DC voltage | $V_{DDIO}$           | +2.5                  | +3.3 | +3.6                  | V     |         |

| power supply  | DC Current | I <sub>VDDIO</sub>   | -                     | 0.35 | 0.50                  | mA    | Note 6  |

| Analog        | DC voltage | V <sub>CI</sub>      | +3.0                  | +3.3 | +3.6                  | V     |         |

| power supply  | DC Current | I <sub>VCI</sub>     | -                     | 13   | 18                    | mA    | Note 6  |

| Permis        | sive input | V <sub>RFVDDIO</sub> | -                     | -    | 100                   | mVp-p | Note 7  |

| Ripple        | voltage    | $V_{RFVCI}$          | -                     | -    | 100                   | mVp-p | Note 7  |

| Logic         | High       | V <sub>IH</sub>      | 0.8 V <sub>DDIO</sub> | -    | V <sub>DDIO</sub>     | V     | Note 8  |

| Input Voltage | Low        | V <sub>IL</sub>      | 0                     |      | 0.2 V <sub>DDIO</sub> | V     | Note 8  |

| Logic         | High       | I <sub>IH</sub>      | -1                    |      | 1                     | μA    | Note 8  |

| Input Current | Low        | I <sub>IL</sub>      | -1                    |      | 1                     | μA    | Note 8  |

Note 6)  $V_{DDIO} = V_{CI} = +3.3V$

Current situation for I<sub>VDDIO</sub>: Black & White checker flag pattern

Current situation for I<sub>VCI</sub>: All black patterns

Note 7)  $V_{DDIO} = V_{CI} = +3.3V$

Note 8) REST, CSB, SDI, SCK, DEN, B7~B0, G7~G0, R7~R0, VSYNC, HSYNC, DOTCLK

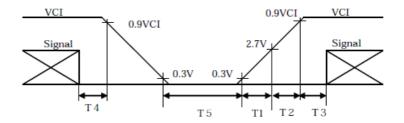

#### Input voltage sequence

0<T1≦15 m s 0<T2≦10 m s 0<T3≦100 m s 0<T4≦1 s T5>200 m s

### 5.2 Driving Backlight

| Item                        | Symbol           | MIN  | TYP  | MAX  | Unit | Remark           |

|-----------------------------|------------------|------|------|------|------|------------------|

| Forward Current             | $I_{\mathrm{F}}$ | -    | 20   | -    | mA   |                  |

| Forward Voltage             | $V_{\mathrm{F}}$ | 17.6 | 19.2 | 20.8 | V    | Constant current |

| Backlight Power consumption | $W_{ m BL}$      | -    | TBD  | -    | W    |                  |

- Note 1: Each LED: IF =20 mA, VF =3.2V.

- Note 2: Optical performance should be evaluated at Ta=25°C only.

- Note 3: If LED is driven by high current, high ambient temperature & humidity condition. The life time of LED will be reduced. Operating life means brightness goes down to 50% initial brightness. Typical operating life time is estimated data.

Figure: LED connection of backlight

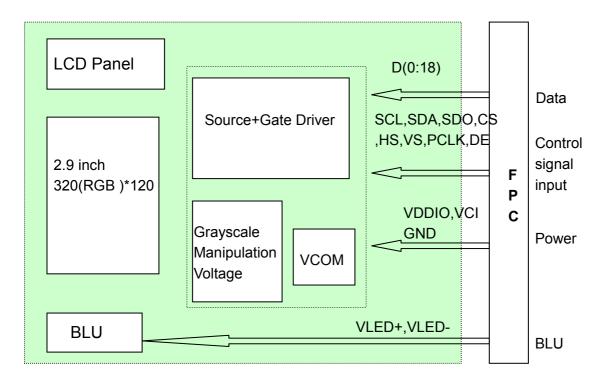

### 5.3 Block Diagram

# 6 Interface Timing

### 6.1 DC Characteristics

| Symbol              | Parameter                                                          | Test Condition                                                                  | Min                      | Тур   | Max                     | Unit   |

|---------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------|-------|-------------------------|--------|

| V <sub>DDEXT</sub>  | System power supply pins of the logic<br>block                     | Recommend Operating Voltage<br>Possible Operating Voltage                       | 1.6                      | -     | 3.6                     | v      |

| $V_{\text{DDIO}}$   | Power supply pin of IO pins                                        | Recommend Operating Voltage<br>Possible Operating Voltage                       | 1.6                      | -     | 3.6                     | v      |

| VcI                 | Booster Reference Supply Voltage<br>Range (3)                      | Recommend Operating Voltage<br>Possible Operating Voltage                       | 2.5 or V <sub>DDIO</sub> | -     | 3.6                     | v      |

| $I_{\text{sleep}}1$ | Sleep mode current (VCI pin)                                       |                                                                                 | -                        | 30    | 50                      | uA     |

| $I_{\text{sleep}}2$ | Sleep mode current<br>(VDDEXT+VDDIO)                               | VDDEXT=VDDIO=1.875V, VCI=2.775V                                                 | -                        | 1     | 50                      | uA     |

| $I_{dp}$            | Operating mode current                                             | 100pF loading at Source output<br>VDDEXT=VDDIO=1.875V, VCI=2.775V               | -                        | 3     | 5                       | mA     |

| $V_{CIM}$           | Negative V <sub>CI</sub> Output Voltage                            | No panel loading                                                                | -V <sub>CI</sub>         | -     | -                       | V      |

| V <sub>CIX2</sub>   | V <sub>CIX2</sub> primary booster efficiency <sup>1</sup>          | No panel loading, ITO for CYP, CYN, VCIX2,<br>VCI and VCHS = 10 Ohm             | 90                       | 95    | 6.1                     | %<br>V |

|                     |                                                                    | No panel loading; 4x booster; ITO for CYP,<br>CYN, VCIX2, VCI and VCHS = 10 Ohm | 84                       | 89.5  | -                       | %      |

| $V_{G\!H}$          | Gate driver High Output Voltage<br>Booster efficiency <sup>2</sup> | No panel loading; 5x booster; ITO for CYP,<br>CYN, VCIX2, VCI and VCHS = 10 Ohm | 80                       | 88.5  | -                       | %      |

|                     |                                                                    | No panel loading; 6x booster; ITO for CYP,<br>CYN, VCIX2, VCI and VCHS = 10 Ohm | 72                       | 80    | -                       | %      |

| $V_{GL}$            | Gate driver Low Output Voltage                                     |                                                                                 | - V <sub>GH</sub>        | -     | -7.3                    | V      |

| $V_{\text{COMH}}$   | VCOM High Output Voltage                                           |                                                                                 | VCI                      | -     | 99% x<br>VLCD63         | v      |

| $V_{COML}$          | VCOM Low Output Voltage                                            |                                                                                 | V <sub>CIM</sub> +0.5    | -     | -                       | V      |

| $V_{\text{COMA}}$   | VCOMA                                                              |                                                                                 | -                        | -     | 6.0 or<br>VCIX2-0.1     | v      |

|                     | VCOM Amplutide V <sub>COMH</sub> - V <sub>COML</sub>               |                                                                                 | -                        | -     | 6.0 or<br>VCIX2-0.1     | v      |

| $V_{LCD63}$         | V <sub>LCD63</sub> Output Voltage <sup>3</sup>                     |                                                                                 | -                        | -     | 6.0 or<br>VCIX2-0.1     | v      |

| $\Delta V_{LCD63}$  | Max. Source Voltage Variation                                      |                                                                                 | -2                       | -     | 2                       | %      |

| VOH1                | Logic High Output Voltage                                          | Iout=-100 A                                                                     | 0.9 * V <sub>DDIO</sub>  | -     | $V_{DDIO}$              | V      |

| VOL1                | Logic Low Output Voltage                                           | Iout=100 A                                                                      | 0                        | -     | 0.1 * V <sub>DDIO</sub> | V      |

| VIH1                | Logic High Input voltage                                           |                                                                                 | 0.8 * V <sub>DDIO</sub>  | -     | $V_{DDIO}$              | V      |

| VIL1                | Logic Low Input voltage                                            |                                                                                 | 0                        | -     | 0.2 * V <sub>DDIO</sub> | V      |

| I <sub>OH</sub>     | Logic High Output Current Source                                   | $Vout = V_{DDIO}-0.4V$                                                          | 50                       | -     | -                       | μA     |

| I <sub>OL</sub>     | Logic Low Output Current Drain                                     | Vout = 0.4V                                                                     | -                        | -     | -50                     | μA     |

| $I_{OZ}$            | Logic Output Tri-state Current Drain<br>Source                     |                                                                                 | -1                       | -     | 1                       | μΑ     |

| $I_{\Pi}/I_{\Pi H}$ | Logic Input Current                                                |                                                                                 | -1                       | -     | 1                       | μA     |

| C <sub>IN</sub>     | Logic Pins Input Capacitance                                       |                                                                                 | -                        | 5     | 7.5                     | pF     |

| R <sub>SON</sub>    | Source drivers output resistance                                   |                                                                                 | -                        | 1     | -                       | kΩ     |

| R <sub>GON</sub>    | Gate drivers output resistance                                     |                                                                                 | -                        | 500   | -                       | Ω      |

| R <sub>CON</sub>    | VCOM output resistance                                             |                                                                                 | -                        | 200   | -                       | Ω      |

| TC                  | Temperature Coefficient                                            |                                                                                 | -                        | -0.01 | _                       | %      |

Notel:

$$\begin{split} &V_{\text{CIX2}} \text{ efficiency} = V_{\text{CIX2}} / (2 \text{ x } V_{\text{CI}}) \text{ x } 100\% \\ &V_{\text{GH}} \text{ efficiency} = V_{\text{GH}} / (V_{\text{CI}} \text{ x } \text{ n}) \text{ x } 100\% \\ &V\text{CIX2} - VL\text{CD63} \ge 0.1V \end{split}$$

Note2: (where n = booster factor)

Note3:

### 6.2 AC Characteristics

AC Characteristics (Unless otherwise specified, Voltage Referenced to  $V_{SS}$ ,  $V_{DDIO} = 1.875V$ ,  $T_A = -40$  to  $85^{\circ}C$ )

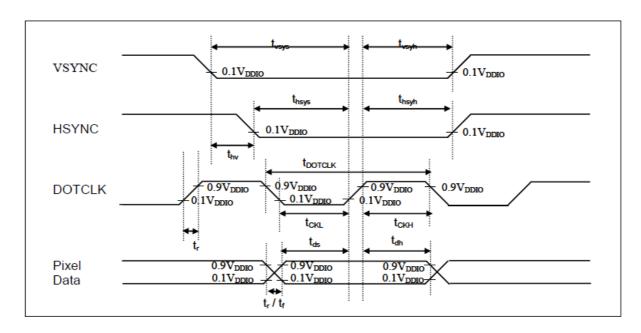

Figure 15-1- Pixel Clock Timing

| Characteristics                                 | Symbol              | Min | Тур | Max | Units               |

|-------------------------------------------------|---------------------|-----|-----|-----|---------------------|

| DOTCLK Frequency                                | f <sub>DOTCLK</sub> | -   | 5.0 | 8.6 | MHz                 |

| DOTCLK Period                                   | t <sub>DOTCLK</sub> | 116 | 200 | -   | nSec                |

| Vertical Sync Setup Time                        | t <sub>vsys</sub>   | 20  | 1   | -   | nSec                |

| Vertical Sync Hold Time                         | $t_{vsyh}$          | 20  | -   | -   | nSec                |

| Horizontal Sync Setup Time                      | t <sub>hsys</sub>   | 20  | -   | -   | nSec                |

| Horizontal Sync Hold Time                       | t <sub>hsyh</sub>   | 20  | -   | -   | nSec                |

| Phase difference of Sync Signal Falling<br>Edge | $t_{ m hv}$         | 0   | -   | 320 | t <sub>DOTCLK</sub> |

| DOTCLK Low Period                               | t <sub>CKL</sub>    | 58  | -   | -   | nSec                |

| DOTCLK High Period                              | t <sub>CKH</sub>    | 58  | -   | -   | nSec                |

| Data Setup Time                                 | t <sub>ds</sub>     | 30  | -   | -   | nSec                |

| Data hold Time                                  | t <sub>dh</sub>     | 30  | -   | -   | nSec                |

| Reset pulse width                               | t <sub>RES</sub>    | 10  | -   | -   | uSec                |

| Rise / Fall time                                | $t_r / t_f$         | -   | -   | 100 | nSec                |

Note: External clock source must be provided to DOTCLK pin of SSD2116Z. The driver will not operate if absent of the clocking signal.

H<sub>cycle</sub> = 336 -HDISP = 320  $t_{HFP} = 8$ **HYSNC** DEN Pixel ---- D317 D318 D319 Dummy Dummy Data a) Horizontal Data Transaction Timing V<sub>cycle</sub> = 244 Lines  $t_{VBP} = 2$ **VYSNC**  $t_{VFP} = 2$ VDISP = 240 Lines **HSYNC** Line 0 Line 239 DEN b) Vertical Data Transaction Timing

Figure 15-2 Data Transaction Timing in Normal Operating Mode (262k-color)

| Characteristics              | Symbol              | Min    | Тур  | Max        | Unit    |

|------------------------------|---------------------|--------|------|------------|---------|

| DOTCLK Frequency             | f <sub>DOTCLK</sub> | [-]    | 5.0  | 8.6        | MHz     |

| DOTCLK Period                | t <sub>DOTCLK</sub> | 116    | 200  | 1531       | nSec    |

| Horizontal Frequency (Line)  | $f_{H}$             | (1-)   | 14.9 | (2)        | kHz     |

| Vertical Frequency (Refresh) | $f_V$               | 85     | 60.9 | 17.1       | Hz      |

| Horizontal Back Porch        | t <sub>HBP</sub>    |        | 8    | 121        | tDOTCLK |

| Horizontal Front Porch       | t <sub>HFP</sub>    |        | 8    | -          | tDOTCLK |

| Horizontal Data Start Point  | t <sub>HBP</sub>    | 102    | 8    | 2          | tDOTCLK |

| Horizontal Blanking Period   | $t_{HBP} + t_{HFP}$ | -      | 16   | -          | tDOTCLK |

| Horizontal Display Area      | HDISP               |        | 320  | 11=1       | tDOTCLK |

| Horizontal Cycle             | H <sub>cycle</sub>  | 12     | 336  | 511        | tDOTCLK |

| Vertical Back Porch          | $t_{\mathrm{VBP}}$  | 10.70  | 2    | 126        | Line    |

| Vertical Front Porch         | t <sub>VFP</sub>    | ( 102) | 2    | 126        | Line    |

| Vertical Data Start Point    | $t_{\mathrm{VBP}}$  |        | 2    | 126        | Line    |

| Vertical Blanking Period     | $t_{VBP} + t_{VFP}$ | 100    | 4    | 252        | Line    |

| Vertical Display Area        | VDISP               | 12     | 240  | ( <u>1</u> | Line    |

| Vertical Cycle               | $V_{cycle}$         | 8-0    | 244  | 553        | Line    |

V<sub>cycle</sub> = 244 Lines

V<sub>cycle</sub> = 244 Lines

VDISP = 240 Lines

t<sub>VFP</sub> = 2

HSYNC

Line 0

VPBP

VPDSP

DEN

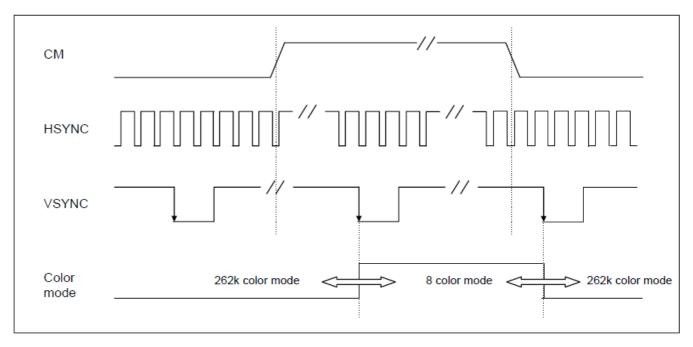

Figure 15-3- Synchronization Signals Timing in Power Save Mode (8 color)

| Characteristics              | Symbol              | Min | Тур  | Max | Units |

|------------------------------|---------------------|-----|------|-----|-------|

| DOTCLK Frequency             | f <sub>DOTCLK</sub> | -   | 5.0  | 8.6 | MHz   |

| DOTCLK Period                | t <sub>DOTCLK</sub> | 116 | 200  | -   | nSec  |

| Horizontal Frequency (Line)  | $\mathbf{f}_{H}$    | -   | 14.9 | -   | kHz   |

| Vertical Frequency (Refresh) | $f_V$               | -   | 60.9 | -   | Hz    |

| Vertical Partial Back Porch  | VPBP                | 0   | 626  | 239 | Line  |

| Vertical Active Area         | VPDSP               | 1   | 9-1  | 240 | Line  |

| Vertical Back Porch          | t <sub>VBP</sub>    | -   | 2    | 126 | Line  |

| Vertical Front Porch         | t <sub>VFP</sub>    | -   | 2    | 126 | Line  |

| Vertical Display Area        | VDISP               | -   | 240  | -   | Line  |

| Vertical Cycle               | V <sub>cycle</sub>  | -   | 244  | -   | Line  |

Note: When entered to 8-color display mode, the RGB graphic data through the interface pins RR5, GG5 and BB5 are valid within the Vertical Active Area. Data "0" will be displayed outside the Vertical Active Area.

Figure 15-4- Color Mode Conversion Timing

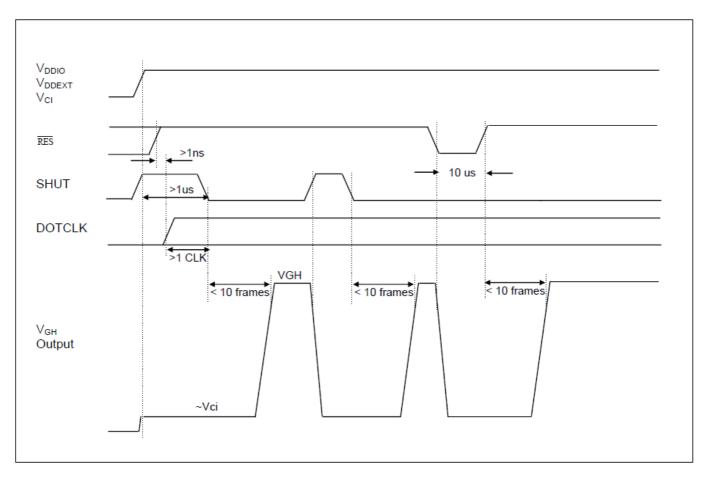

Figure 15-5- VGH Output against SHUT & RESB

Notel: The minimum cycle time of SHUT is 10 + 2 frames.

Note2: DOTCLK must be provided for boosting of  $V_{GH}$ . The above timing diagram assumed voltages and DOTCLK are

continuous supplied after power on.

Note3:  $V_{GH}$  will be forced to  $V_{Gi}$  at the low stage of  $\overline{RES}$ .

Note4: The minimum pulse width of RESET is 10us.

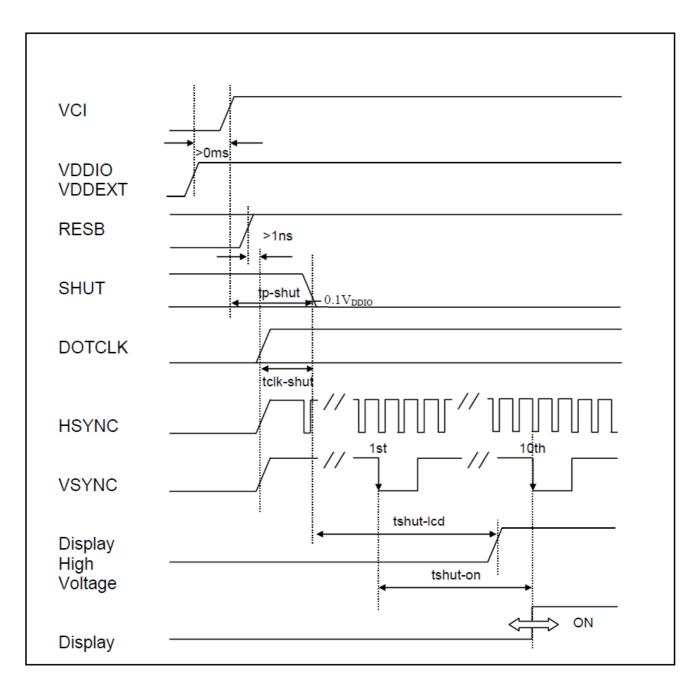

Figure 15-6 - Power Up Sequence

| Characteristics                                                   | Symbol    | Min | Тур | Max | Units |

|-------------------------------------------------------------------|-----------|-----|-----|-----|-------|

| V <sub>DDEXT</sub> / V <sub>DDIO</sub> on to falling edge of SHUT | tp-shut   | 1   | -   | -   | μsec  |

| DOTCLK                                                            | telk-shut | 1   | -   | -   | clk   |

| Falling edge of SHUT to LCD power on                              | tshut-lcd | -   | -   | 164 | msec  |

| Falling edge of SHUT to display start                             |           | -   | -   | 10  | frame |

| 1 line: 336 clk                                                   | tshut-on  |     |     |     |       |

| 1 frame: 244 line                                                 | tshut-on  | -   | 164 | -   | msec  |

| DOTCLK = 5.0MHz                                                   |           |     |     |     |       |

Note1: It is necessary to input DOTCLK before the falling edge of SHUT.

Note2: Display starts at  $10^{th}$  falling edge of VSTNC after the falling edge of SHUT.

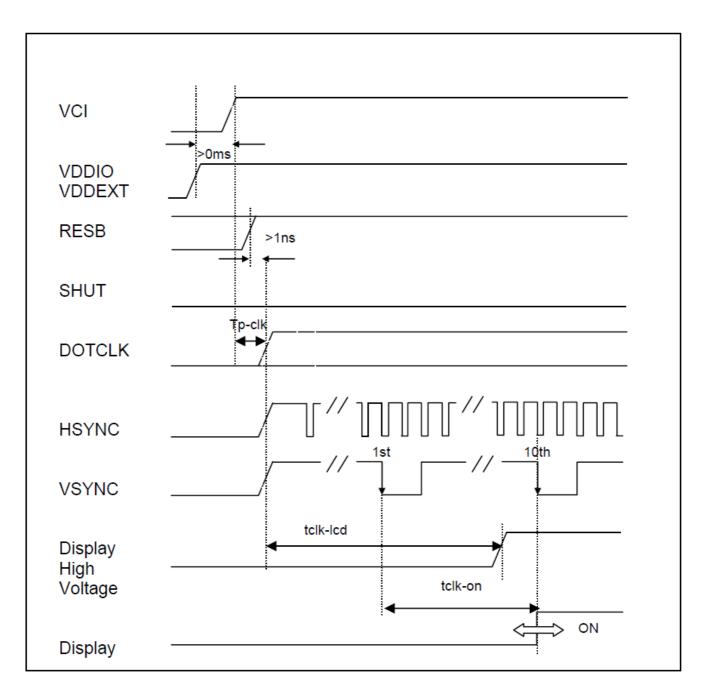

Figure 15-7 - Power Up Sequence (Shut pin tied to ground)

| Characteristics                                                    | Symbol   | Min | Тур | Max | Units |

|--------------------------------------------------------------------|----------|-----|-----|-----|-------|

| V <sub>DDEXT</sub> / V <sub>DDIO</sub> on to rising edge of Dotclk | tp-clk   | 1   | -   | -   | μsec  |

| Rising edge of Dotclk to LCD power on                              | tclk-lcd | -   | -   | 164 | msec  |

| Rising edge of Dotclk to display start                             |          | -   | -   | 10  | frame |

| 1 line: 336 clk<br>1 frame: 244 line                               | tclk-on  | -   | 164 | -   | msec  |

| DOTCLK = 5.0MHz                                                    |          |     |     |     |       |

Note1: Display starts at 10<sup>th</sup> falling edge of VSYNC after the rising edge of DOTCLK.

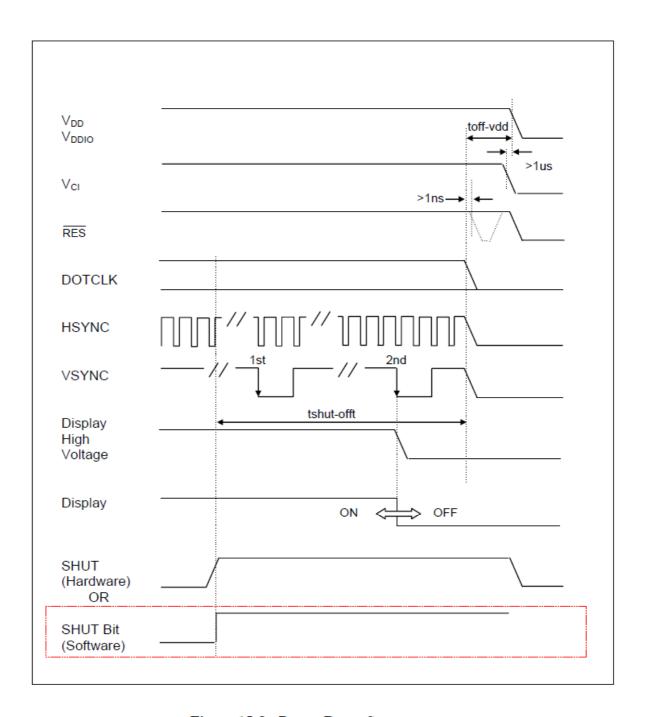

Figure 15-8 - Power Down Sequence

| Characteristics                                                | Symbol    | Target<br>Min | Target<br>Typ | Target<br>Max | Units |

|----------------------------------------------------------------|-----------|---------------|---------------|---------------|-------|

| Rising edge of SHUT to display off 1 line: 336 clk             | 4-14 - 66 | 2             | -             | -             | frame |

| 1 frame: 244 line<br>PIXCLK = 5.0 MHz                          | tshut-off | 32.8          | -             | -             | msec  |

| Input-signal-off to V <sub>DDEXT</sub> / V <sub>DDIO</sub> off | toff-vdd  | 1             | -             | -             | μsec  |

Notel: DOTCLK must be maintained at lease 2 frames after the rising edge of SHUT.

Note2: Display become off at the 2<sup>nd</sup> falling edge of VSTNC after the falling edge of SHUT.

Note3: If RESET signal is necessary for power down, provide it after the 2-frames-cycle of the SHUT period.

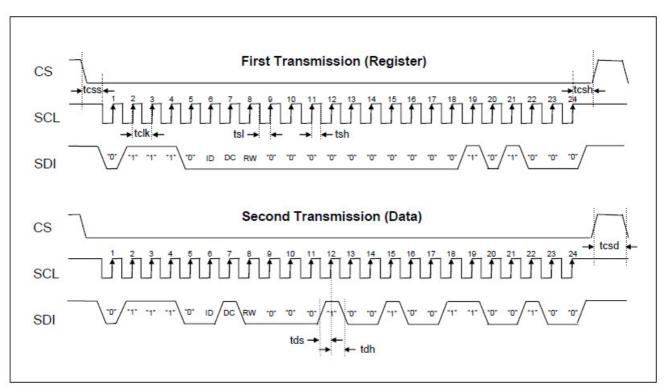

Figure 15-9 - SPI Interface Timing Diagram & Transaction Example

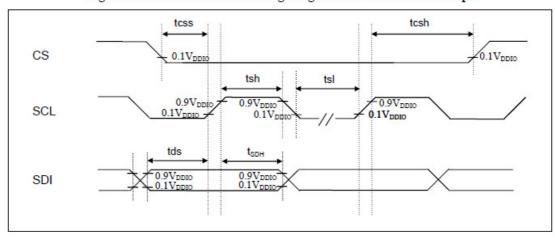

Figure 15-10 - SPI Interface Timing Diagram

| Characteristics             | Symbol | Min | Тур   | Max | Units |

|-----------------------------|--------|-----|-------|-----|-------|

| Serial Clock Frequency      | fclk   | -   | 550   | 20  | MHz   |

| Serial Clock Cycle Time     | tclk   | 50  | -     | -   | nsec  |

| Clock Low Width             | ts1    | 25  | (2)   | =   | nsec  |

| Clock High Width            | tsh    | 25  | 125   |     | nsec  |

| Chip Select Setup Time      | tcss   | 0   | 55-03 | -   | nsec  |

| Chip Select Hold Time       | tcsh   | 10  | 98    | -   | nsec  |

| Chip Select High Delay Time | tcsd   | 20  |       | -   | nsec  |

| Data Setup Time             | tds    | 5   | 1218  | 2   | nsec  |

| Data Hold Time              | tdh    | 10  | 858   |     | nsec  |

Notel: The example transmit "0x1264h" to register R28h.

Note2: SPID pin connected to VSS.

# 7 Optical Characteristics

| Items          |             | Symbol       | Condition | Min. | Typ. | Max. | Unit    | Remark          |  |

|----------------|-------------|--------------|-----------|------|------|------|---------|-----------------|--|

|                |             |              |           | -    | 40   | -    |         |                 |  |

| Viewing angles |             | $\theta_{B}$ | Center    | -    | 60   | -    | Dagraa  | Note2           |  |

| viewing ang    | ies         | $\theta_{L}$ | CR≥10     | ı    | 60   | -    | Degree. | Notez           |  |

|                |             | $\theta_{R}$ |           | ı    | 60   | -    |         |                 |  |

| Contrast Rat   | io          | CR           | ⊖ =0      | 100  | 300  | -    | -       | Note1,<br>Note3 |  |

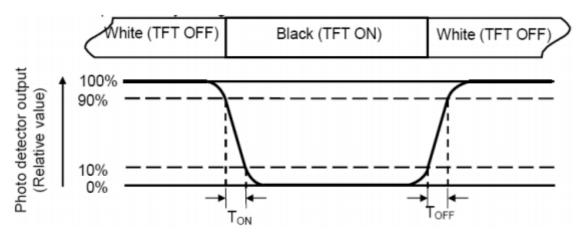

| Dogmongo Tie   |             | Ton          | 25° C     | -    | 30   | 45   | 400.0   | Note1,          |  |

| Response Ti    | ne          | $T_{OFF}$    | 25 C      | -    | 30   | 45   | ms      | Note4           |  |

|                | White       | $X_{W}$      |           | 0.25 | 0.30 | 0.35 | -       |                 |  |

|                | willte      | $Y_{W}$      |           | 0.27 | 0.32 | 0.37 | -       |                 |  |

|                | Red         | $X_R$        |           | 0.52 | 0.57 | 0.62 | -       |                 |  |

| Chromoticity   | Red         | $Y_R$        | Backlight | 0.26 | 0.31 | 0.36 | -       | Note1,          |  |

| Chromaticity   | Craan       | $X_{G}$      | is on     | 0.29 | 0.34 | 0.39 | -       | Note5           |  |

|                | Green       | $Y_{G}$      |           | 0.50 | 0.55 | 0.60 | -       |                 |  |

|                | Blue        | $X_{B}$      |           | 0.10 | 0.15 | 0.20 | -       |                 |  |

|                | Diue        | $Y_B$        |           | 0.05 | 0.10 | 0.15 | -       |                 |  |

| Uniformity     | ,           | U            |           | 75   | 80   | -    | %       | Note1,<br>Note6 |  |

| NTSC           |             |              |           |      | 50   |      | %       | Note5           |  |

| Luminance      | <del></del> | L            |           | -    | 300  | _    |         | Note1,<br>Note7 |  |

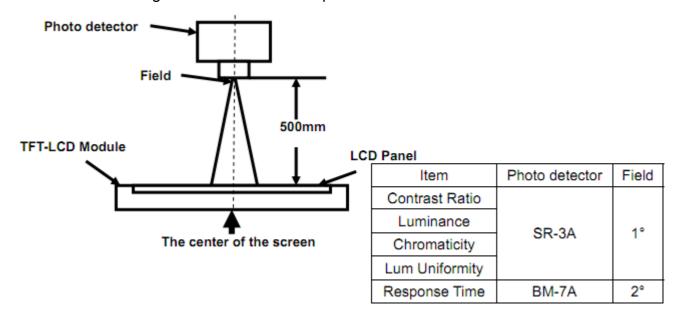

#### **Test Conditions:**

- 1. IF= 20mA(one channel), the ambient temperature is 25

- 2. The test systems refer to Note 1 and Note 2.

#### Note 1:Definition of optical measurement system.

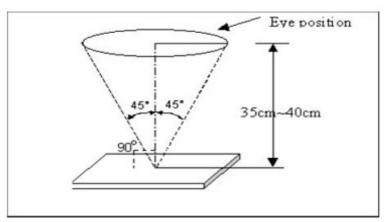

The optical characteristics should be measured in dark room. After 5 minutes operation, the optical properties are measured at the center point of the LCD screen. All input terminals LCD panel must be ground when measuring the center area of the panel.

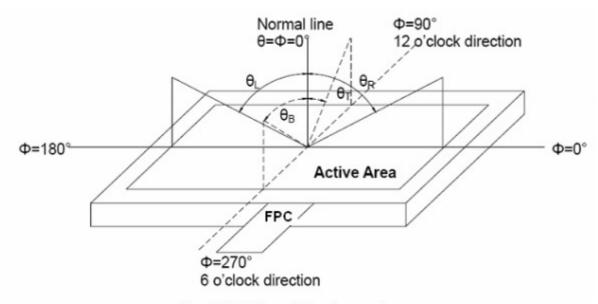

Note 2: Definition of viewing angle range and measurement system. viewing angle is measured at the center point of the LCD by CONOSCOPE(ergo-80).

Fig. 1 Definition of viewing angle

#### Note 3: Definition of contrast ratio

Contrast ratio (CR) = Luminance measured when LCD is on the "White" state

Luminance measured when LCD is on the "Black" state

"White state ":The state is that the LCD should driven by Vwhite.

"Black state": The state is that the LCD should driven by Vblack.

Vwhite: To be determined Vblack: To be determined.

#### Note 4: Definition of Response time

The response time is defined as the LCD optical switching time interval between "White" state and "Black" state. Rise time (TON) is the time between photo detector output intensity changed from 90% to 10%. And fall time (TOFF) is the time between photo detector output intensity changed from 10% to 90%.

Note 5: Definition of color chromaticity (CIE1931) Color coordinates measured at center point of LCD.

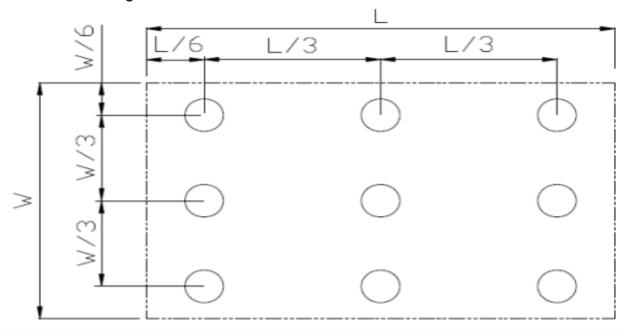

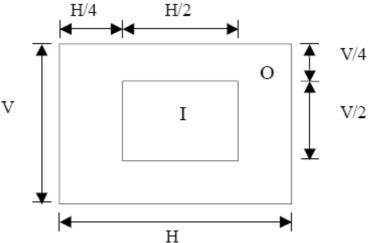

#### Note 6: Definition of Luminance Uniformity

Active area is divided into 9 measuring areas (Refer Fig. 2). Every measuring point is placed at the center of each measuring area.

Luminance Uniformity(U) = Lmin/Lmax

L-----Active area length W----- Active area width

Fig. 2 Definition of uniformity

Lmax: The measured maximum luminance of all measurement position. Lmin: The measured minimum luminance of all measurement position.

#### Note 7: Definition of Luminance:

Measure the luminance of state at point.

# 8 Environmental / Reliability Tests

| No | Test Item                                                           | Condition                                          | Remarks               |

|----|---------------------------------------------------------------------|----------------------------------------------------|-----------------------|

|    | High Temperature                                                    |                                                    | Note 1                |

| 1  | Operation                                                           | $T_S = +70^{\circ}C$ , 120hrs                      | IEC60068-2-2,         |

|    | operation                                                           |                                                    | GB2423. 2-89          |

| 2  | Low Temperature                                                     | Ta= -20°C, 120hrs                                  | Note 2 IEC60068-2-1   |

|    | Operation                                                           | 1a -20 C, 120ms                                    | GB2423.1-89           |

| 3  | High Temperature                                                    | $Ta = +80^{\circ}C, 240 hrs$                       | IEC60068-2-2          |

| 3  | Storage                                                             | 1a- +80 C, 240ms                                   | GB2423. 2-89          |

| 4  | Low Temperature                                                     | 1a = -30 (1.740) hrs                               |                       |

| 4  | Storage                                                             | orage 1a= -30 C, 240nrs                            |                       |

| 5  | High Temperature & $Ta=+60^{\circ}\text{C}$ , 90% RH max, 160 hours |                                                    | IEC60068-2-3          |

| 3  | Humidity Storage                                                    | 1a− ±00 €, 90% KH Illax, 100 llouis                | GB/T2423.3-2006       |

|    |                                                                     |                                                    | Start with cold       |

|    | Thermal Shock                                                       | 20°C 20 min 180°C 20 min                           | temperature, end with |

| 6  |                                                                     | $-30^{\circ}$ C 30 min $\sim +80^{\circ}$ C 30 min | high temperature      |

|    | (Non-operation)                                                     | Change time: 5min, 30 Cycle                        | IEC60068-2-14,        |

|    |                                                                     |                                                    | GB2423.22-87          |

|    |                                                                     | C=150pF, R=330 $\Omega$ , 5 points/panel           |                       |

| 7  | Electro Static Discharge                                            | Air: $\pm 8$ KV, 5 times; Contact: $\pm 4$ KV,     | IEC61000-4-2          |

| 7  | (Opeartion)                                                         | 5 times; (Environment: 15°C ∼                      | GB/T17626.2-1998      |

|    |                                                                     | 35°C, 30% ~ 60%, 86Kpa ~ 106Kpa)                   |                       |

|    |                                                                     | Frequency range: 10~55Hz, Stroke:                  |                       |

|    | ATT 1: OI                                                           | 1.mm Sweep: 10Hz~55Hz~10Hz                         | IEC60068-2-6          |

| 8  | Vibration (Non-operation)                                           | 2 hours for each direction of X .Y. Z.             | GB/T2423.5-1995       |

|    |                                                                     | (package condition)                                |                       |

| 9  | Charle (Non anamatic ::)                                            | 60G 6ms, $\pm$ X, $\pm$ Y, $\pm$ Z                 | IEC60068-2-27         |

| 9  | Shock (Non-operation)                                               | 3 times for each direction                         | GB/T2423.5-1995       |

| 10 | Doolsoon Dross Tool                                                 | Height: 80 cm, 1 corner, 3 edges,                  | IEC60068-2-32         |

| 10 | rackage Drop Test                                                   | ckage Drop Test  6 surfaces                        |                       |

Note: 1.  $T_S$  is the temperature of panel's surface.

2. Ta is the ambient temperature of sample.

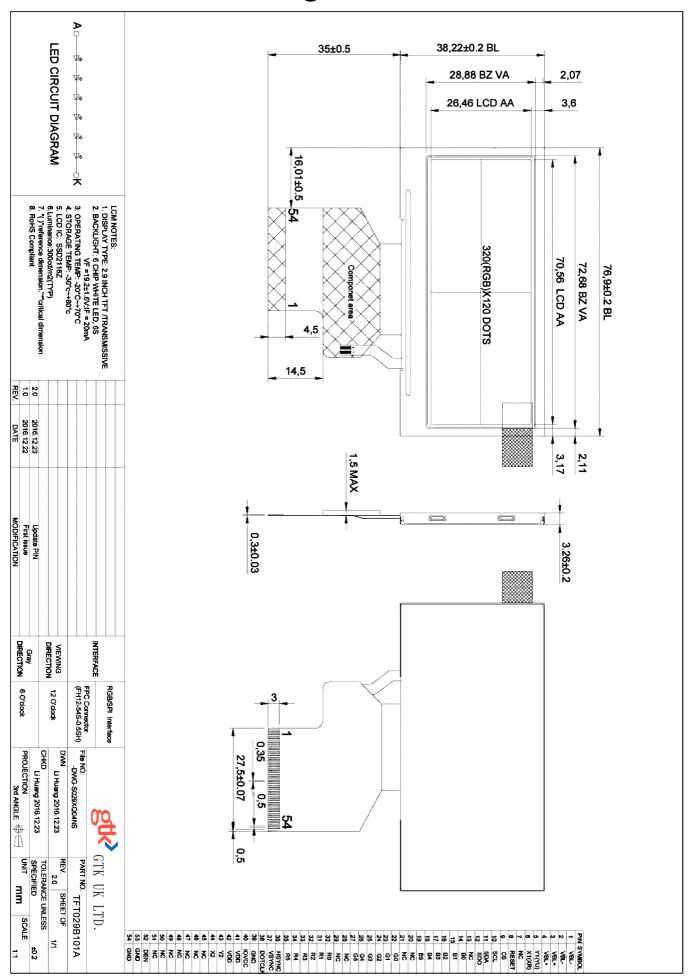

# 9 Mechanical Drawing

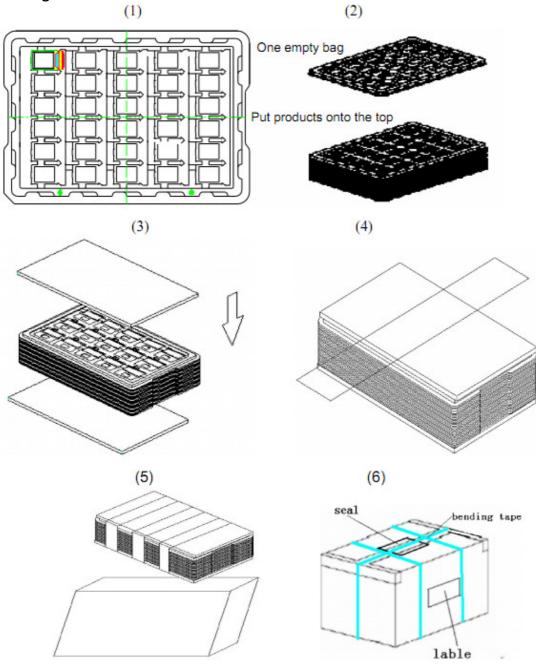

## 1 0.Packing

#### **Packing Method**

- 1. Put module into tray cavity:

- 2. Tray stacking

- 3. Put 1 cardboard under the tray stack and 1 cardboard above:

- 4. Fix the cardboard to the tray stack with adhesive tape:

- 5. Put the tray stack into carton.

- 6. Carton sealing with adhesive tape.

### 11 Precautions For Use of LCD modules

### 11.1 Handling Precautions

- 11.1.1. The display panel is made of glass. Do not subject it to a mechanical shock by dropping it from a high place, etc.

- 11.1.2. If the display panel is damaged and the liquid crystal substance inside it leaks out, be sure not to get any in your mouth, if the substance comes into contact with your skin or clothes, promptly wash it off using soap and water.

- 11.1.3. Do not apply excessive force to the display surface or the adjoining areas since this may cause the color tone to vary.

- 11.1.4. The polarizer covering the display surface of the LCD module is soft and easily scratched. Handle this polarizer carefully.

- 11.1.5. If the display surface is contaminated, breathe on the surface and gently wipe it with a soft dry cloth. If still not completely clear, moisten cloth with one of the following solvents:

- Isopropyl alcohol

- Ethyl alcohol

Solvents other than those mentioned above may damage the polarizer. Especially, do not use the following:

- Water

- Ketone

- Aromatic solvents

- 11.1.6. Do not attempt to disassemble the LCD Module.

- 11.1.7. If the logic circuit power is off, do not apply the input signals.

- 11.1.8. To prevent destruction of the elements by static electricity, be careful to maintain an optimum work environment.

- 11.1.8.1. Be sure to ground the body when handling the LCD Modules.

- 11.1.8.2. Tools required for assembly, such as soldering irons, must be properly ground.

- 11.1.8.3. To reduce the amount of static electricity generated, do not conduct assembly and other work under dry conditions.

- 11.1.8.4. The LCD Module is coated with a film to protect the display surface. Be care when peeling off this protective film since static electricity may be generated.

### 11.2 Storage Precautions

- 12.2.1. When storing the LCD modules, avoid exposure to direct sunlight or to the light of fluorescent lamps.

- 11.2.2. The LCD modules should be stored under the storage temperature range If the LCD modules will be stored for a long time, the recommend condition is:

Temperature : 0°C ~ 40°C Relatively humidity: ≤80%

11.2.3. The LCD modules should be stored in the room without acid, alkali and harmful gas.

### 11.3 Inspection Sampling

3.1. Lot size: Quantity per shipment lot per model

3.2. Sampling type: Normal inspection, Single sampling

3.3. Inspection level: II

3.4. Sampling table: MIL-STD-105D

3.5. Acceptable quality level (AQL)

Major defect : AQL=0.65 Minor defect: AQL=1.00

### 11.4 Inspection Conditions

4.1 Ambient conditions:

a. Temperature: Room temperature  $25\pm5\,^{\circ}\mathrm{C}$

b. Humidity: (60 $\pm$ 10) %RH

c. Illumination: Single fluorescent lamp non-directive (300 to 700 Lux)

4.2 Viewing distance

The distance between the LCD and the inspector's eyes shall be at least  $35\pm5~$  cm.

4.3 Viewing Angle

U/D: 45o/45o, L/R: 45o/45o

## 11.5. Inspection Criteria

Defects are classified as major defects and minor defects according to the degree of defectiveness defined herein.

## 11.5.1 Major defect

| Item No | Items to be inspected     | Inspection Standard                                                 |

|---------|---------------------------|---------------------------------------------------------------------|

| 5.1.1   | All functional<br>defects | 1) No display 2) Display abnormally 3) Short circuit 4) line defect |

| `5.1.2  | Missing                   | Missing function component                                          |

| 5.1.3   | Crack                     | Glass Crack                                                         |

### 11.5.2 Minor defect

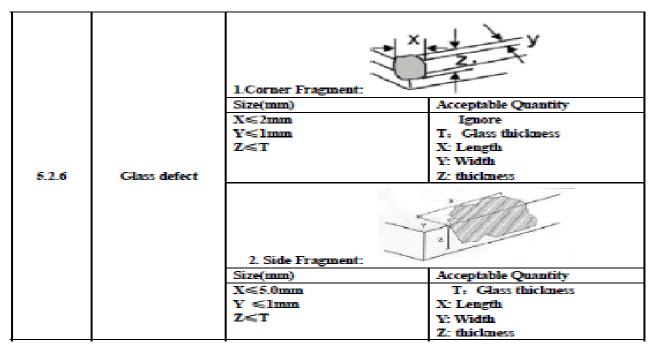

| Item No | Items to be inspected                                | Inspection standard                                                                                                                                                                                         |                     |  |  |

|---------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--|--|

| 5.2.1   | Spot Defect<br>Including<br>Black spot<br>White spot | For dark/white spot is defined $\varphi = (x+y) / 2$ $\xrightarrow{X} \qquad \qquad$ |                     |  |  |

|         | Pinhole                                              | Size φ(mm)                                                                                                                                                                                                  | Acceptable Quantity |  |  |

|         | Foreign                                              | φ≤0.10                                                                                                                                                                                                      | Ignore              |  |  |

|         | particle                                             | $0.10 < \phi \leq 0.2$                                                                                                                                                                                      |                     |  |  |

|         |                                                      | 0.2 < φ Not allowed                                                                                                                                                                                         |                     |  |  |

| 5.2.2 | Polarizer dirt,<br>particle        | Size o(mm)                                                                 | Acceptab    | le Quantity  |  |  |

|-------|------------------------------------|----------------------------------------------------------------------------|-------------|--------------|--|--|

|       | particular                         | φ≤0.15                                                                     | 1           |              |  |  |

|       | Line Defect                        | Define:                                                                    | h           |              |  |  |

| 5.2.3 | Including Black<br>line White line | Width(mm)<br>Length(mm)                                                    | Acceptal    | ble Quantity |  |  |

|       | Scratch                            | W≤0.05                                                                     | Ig          | gnore        |  |  |

|       |                                    | 0.05 < W≤0.1<br>L≤1.5                                                      |             | 2            |  |  |

|       | 0.1 < W, or L>1.5                  | Not                                                                        | allowed     |              |  |  |

| 5.2.4 | Polarizer<br>Dent/Bubble           | Not a                                                                      | llowed      |              |  |  |

|       |                                    | 平利<br>and                                                                  |             |              |  |  |

| 5.2.5 | Electrical Dot<br>Defect           | Two Adjace                                                                 |             |              |  |  |

|       |                                    | Inspection pattern: Full white. Full black. Red. green and<br>blue screens |             |              |  |  |

|       |                                    | Item                                                                       |             | ole Quantity |  |  |

|       |                                    |                                                                            | I O         | Note         |  |  |

|       |                                    | Black dot defect                                                           | 2           | 5mm ≤Distant |  |  |

|       |                                    | Bright dot defect                                                          | 1           |              |  |  |

|       |                                    | Two Adjacent Dot                                                           | 1           | THE STATE    |  |  |

|       |                                    | There or more Adjacent Dot                                                 | Not allowed |              |  |  |

|       | 40                                 | Total Dot                                                                  | 2           |              |  |  |

Note: 1). Dot defect is defined as the defective area of the dot area is larger than 50% of the dot area.

- 2). The distance between two bright dot defects (red, green, blue, and white) should be larger than 15mm.

- 3). The distance between black dot defects or black and bright dot defects should be more than 5mm apart.

- 4). Polarizer bubble is defined as the bubble appears on active display area. The defect of polarizer bubble shall be ignored if the polarizer bubble appears on the outside of active display area.

## 11.6 Mechanics specification

As for the outside dimension of the modules, please refer to product specification for more details

Note:

- 1). Dot defect is defined as the defective area of the dot area is larger than 50% of the dot area.

- 2). The distance between two bright dot defects (red, green, blue, and white)