# SPECIFICATION FOR TFT MODULE

**MODULE NO. : IPS078A110A**

**CUSTOMER NO.:**

Rev No.: O

| gтĸ       | PREPARED BY | CHECKED BY | APPROVED BY |

|-----------|-------------|------------|-------------|

| SIGNATURE | 薛俊鑫         | 郭金明        | Tray. Zhou  |

| DATE      | 2020.12.07  | 2020.12.07 | 2020.12.07  |

|                      | SIGNATURE | DATE |

|----------------------|-----------|------|

| CUSTOMER<br>APPROVAL |           |      |

#### Notes:

- 1. Please contact GTK before assigning your product based on this module specification.

- 2. To improve the quality of product, and this product specification is subject to change without any notice.

| O 2020-12-07 First release Preliminary |

|----------------------------------------|

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

|                                        |

| 1. GENERAL INFORMATION               | 3  |

|--------------------------------------|----|

| 2. ABSOLUTE MAXIMUM RATINGS          | 3  |

| 3. ELECTRICAL CHARACTERISTICS        | 4  |

| 4. BACKLIGHT CHARACTERISTICS         | 4  |

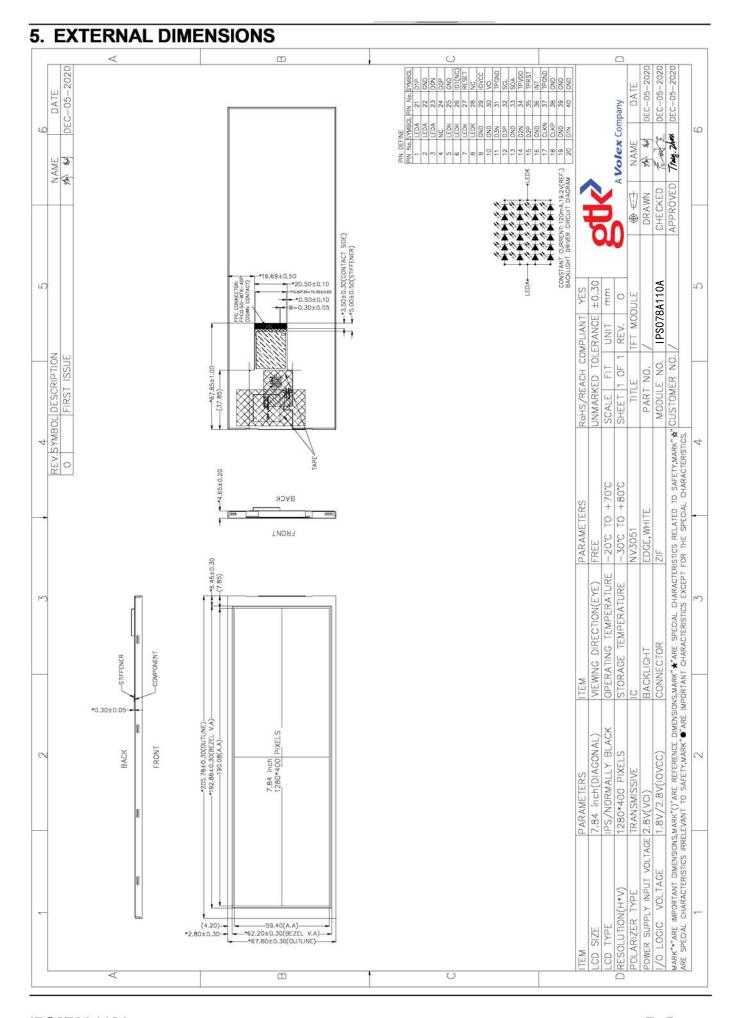

| 5. EXTERNAL DIMENSIONS               | 5  |

| 6. ELECTRO - OPTICAL CHARACTERISTICS | 6  |

| 7. INTERFACE DESCRIPTION             | 8  |

| 8.AC CHARACTERISTICS                 | 9  |

| 9. POWER SEQUENCE                    | 14 |

| 10. RELIABILITY TEST CONDITIONS      | 16 |

| 11.INSPECTION CRITERION              | 17 |

| 12. HANDLING PRECAUTIONS             | 24 |

| 13. PRECAUTION FOR USE               | 25 |

| 14. PACKING SPECIFICATION            | 25 |

| 15. INITIALIZATION CODE              | 26 |

| 16 HSF COMPLIANCE                    | 29 |

# 1. GENERAL INFORMATION

| No. | Item                           | Contents                        | Unit |

|-----|--------------------------------|---------------------------------|------|

| 1   | LCD size                       | 7.84 inch (Diagonal)            | /    |

| 2   | Display mode                   | IPS/Normally black/Transmissive | /    |

| 3   | Viewing direction(eye)         | Free                            | /    |

| 4   | Gray scale inversion direction | -                               | /    |

| 5   | Resolution(H*V)                | 1280*400 Pixels                 | /    |

| 6   | Module size (L*W*H)            | 205.78*67.80*4.65               | mm   |

| 7   | Active area (L*W)              | 190.08*59.40                    | mm   |

| 8   | Pixel pitch (L*W)              | 0.1485*0.1485                   | mm   |

| 9   | Interface type                 | MIPI interface                  | /    |

| 10  | Color Depth                    | 16.7M                           | /    |

| 11  | Module power consumption       | TBD                             | W    |

| 12  | Back light type                | LED                             | /    |

| 13  | Driver IC                      | NV3051                          | /    |

| 14  | Weight                         | TBD                             | G    |

# 2. ABSOLUTE MAXIMUM RATINGS

| Item                               | Symbol | Min. | Max. | Unit | Note  |

|------------------------------------|--------|------|------|------|-------|

| Power supply input voltage for TFT | VDD    | -0.3 | 5.0  | V    |       |

| Backlight current (normal temp.)   | ILED   | -    | 150  | mA   |       |

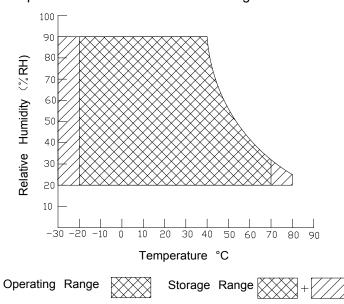

| Operation temperature              | Тор    | -20  | +70  | °C   | Note1 |

| Storage temperature                | Tst    | -30  | +80  | °C   | Note1 |

| Humidity                           | RH     | -    | 90%  | RH   | Note1 |

#### Note1:

1). The relative humidity and temperature range are as below sketch, 90%RH Max.

2). The maximum wet bulb temperature  $\leq$  40  $^{\circ}$ C and without dewing.

QÚÙ€ÏÌŒFF€ŒP.3

# 3. ELECTRICAL CHARACTERISTICS

DC CHARACTERISTICS(at Ta=25°C)

| Item                                   | Symbol | Min.     | Тур. | Max.     | Unit | Note  |

|----------------------------------------|--------|----------|------|----------|------|-------|

| Power supply input voltage             | VDD    | 2.5      | 2.8  | 3.6      | ٧    |       |

| I/O logic voltage                      | VDDIO  | 1.65     | 1.8  | 3.6      | ٧    |       |

| Input voltage 'H' level                | VIH    | 0.7VDDIO | -    | VDDIO    | V    |       |

| Input voltage 'L' level                | VIL    | VSS      | -    | 0.3VDDIO | V    |       |

| Power supply current                   | IVDD   | -        | TBD  | -        | mA   |       |

| TFT gate on voltage                    | VGH    | -        | -    | -        | V    |       |

| TFT gate off voltage                   | VGL    | -        | -    | -        | ٧    |       |

| Analog power supply voltage            | AVDD   | -        | -    | -        | V    |       |

| Differential input common mode voltage | Vcom   | -        | -    | -        | V    | Note1 |

Note1: The value is just the reference value. The customer can optimize the setting value by the different D-IC Vcom must be adjusted to optimize display quality, as Crosstalk and Contrast Ratio etc..

# 4. BACKLIGHT CHARACTERISTICS

(at Ta=25°C,RH=60%)

| Item                  | Symbol | Min.                      | Тур.  | Max.   | Unit | Note      |

|-----------------------|--------|---------------------------|-------|--------|------|-----------|

| LED forward voltage   | VF     | 16.8                      | 19.2  | 20.4   | V    |           |

| LED forward current   | IF     | -                         | 120   | -      | mA   | IF=30*4mA |

| LED power consumption | PLED   | -                         | 2.304 | -      | W    | Note1     |

| Number of LED         | -      |                           | 24    |        | PCS  |           |

| Connection mode       | -      | 6 in series 4 in parallel |       | rallel | 1    |           |

| LED life-time         | -      | 20000                     | -     | -      | Hrs  | Note2     |

Note1 : Calculator value for reference : IF\*VF = PLED

Note2: The LED life-time define as the estimated time to 50% degradation of initial brightness at Ta=25°C and IF =120mA. The LED lifetime could be decreased if operating IF is larger than 120mA.

QÚÙ€ÏÌŒF€Œ P.4

#### 6. ELECTRO - OPTICAL CHARACTERISTICS

| Item                 | Symbol          | Condition    | Min.  | Тур. | Max.  | Unit              | Remark  | Note   |

|----------------------|-----------------|--------------|-------|------|-------|-------------------|---------|--------|

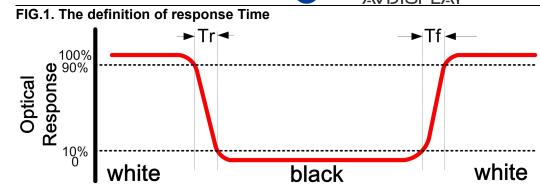

| Response time        | Tr+ Tf          |              | -     | 30   | 35    | ms                | FIG.1   | Note 1 |

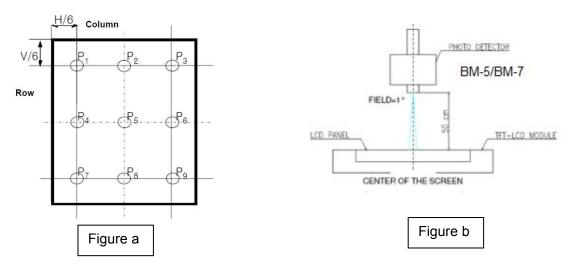

| Contrast ratio       | Cr              | -            | 700   | 900  | -     | -                 | FIG.2   | Note 2 |

| Surface<br>luminance | Lv              | θ=0°         | 400   | 500  | -     | cd/m <sup>2</sup> | FIG.2   | Note 3 |

| Luminance uniformity | Yu              | θ=0°         | 70    | 80   | -     | %                 | FIG.2   | Note 4 |

| NTSC                 | -               | θ=0°         | -     | 50   | -     | %                 | FIG.2   | Note 5 |

| Viewing angle        |                 | ∅=90°        | 70    | 80   | -     | deg               | FIG.3   | Note 6 |

|                      | /iewing angle θ | ∅=270°       | 70    | 80   | -     | deg               | FIG.3   |        |

|                      |                 | ∅=0°         | 70    | 80   | -     | deg               | FIG.3   |        |

|                      |                 | ∅=180°       | 70    | 80   | -     | deg               | FIG.3   |        |

|                      | Red x           |              |       | TBD  |       | -                 |         |        |

|                      | Red y           |              | ı     | TBD  |       | -                 | FIG.2   | Note 5 |

|                      | Green x         | 0.00         |       | TBD  |       | -                 |         |        |

| CIE (x,y)            | Green y         | θ=0°<br>∅=0° | Тур   | TBD  | Тур   | -                 |         |        |

| chromaticity         | Blue x          | <br>Ta=25°C  | -0.04 | TBD  | +0.04 | -                 | CIE1931 | Note 5 |

|                      | Blue y          | 14 20 0      |       | TBD  |       | -                 |         |        |

|                      | White x         |              |       | TBD  |       | -                 |         |        |

|                      | White y         |              |       | TBD  |       | -                 |         |        |

#### Note1. Definition of response time

The response time is defined as the LCD optical switching time interval between "White" state and "Black" state. Rise time  $(T_{ON})$  is the time between photo detector output intensity changed from 90% to 10%. And fall time  $(T_{OFF})$  is the time between photo detector output intensity changed from 10% to 90%. For additional information see FIG1.

#### Note2.Definition of contrast ratio

Contrast ratio(Cr) is defined mathematically by the following formula.

For more information see FIG.2.

Contrast ratio= Luminance measured when LCD on the "White" state

Luminance measured when LCD on the "Black" state

Measured at the center area of the LCD

#### Note3.Definition of surface luminance

Surface luminance is the luminance with all pixels displaying white.

For more information see FIG.2.

Lv = Average Surface Luminance with all white pixels(P1,P2,P3, .....,Pn)

# Note4.Definition of luminance uniformity

The luminance uniformity in surface luminance is determined by measuring luminance at each test position 1 through n, and then dividing the maximum luminance of n points luminance by minimum luminance of n points luminance. For more information see FIG.2.

$Y_{u} = \frac{\text{Minimum surface luminance with all white pixels (P1,P2,P3,.....,Pn)}}{\text{Maximum surface luminance with all white pixels (P1,P2,P3,.....,Pn)}}$

## Note5. Definition of color chromaticity (CIE1931)

CIE (x,y) chromaticity, The x,y value is determined by screen active area center position P5. For more information see FIG.2.

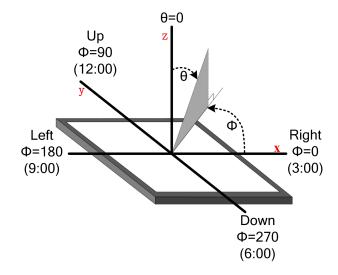

# Note6. Definition of viewing angle

Viewing angle is the angle at which the contrast ratio is greater than 10. angles are determined for the horizontal or x axis and the vertical or y axis with respect to the z axis which is normal to the LCD surface. For more information see FIG.3.

For viewing angle and response time testing, the testing data is base on Autronic-Melchers's ConoScope or DMS series Instruments or compatible. For contrast ratio, Surface Luminance, Luminance uniformity and CIE, the testing data is base on TOPCON's BM-5or BM-7 photo detector or compatible.

QÚÙ€ÏÌŒF€Œ P.6

FIG.1. The definition of response Time

FIG.2. Measuring method for contrast ratio, surface luminance, luminance uniformity, CIE (x,y) chromaticity

H,V: Active area

Light spot size  $\emptyset$  = 5 mm(BM-5) or  $\emptyset$  =7.7mm (BM-7)50cm distance or compatible distance from the LCM surface to detector lens.

Test spot position : see Figure a.

measurement instrument: TOPCON's luminance meter BM-5 or BM-7 or compatible, see Figure b.

FIG.3. The definition of viewing angle

OÚÙ€ÏÌOEFF€Œ P. 7

# 7. INTERFACE DESCRIPTION

**Module Interface description**

| Interface No. | Name    | I/O or connect to | Description                                         |

|---------------|---------|-------------------|-----------------------------------------------------|

| 1-3           | LEDA    | I                 | Anode of Backlight                                  |

| 4             | NC      | 1                 | Open                                                |

| 5-8           | LEDK    | I                 | Cathode of Backlight                                |

| 9-10          | GND     | Р                 | Ground                                              |

| 11            | D3N     | Р                 | MIPI-DSI data Lane 3 negative-end input/output pin  |

| 12            | D3P     | Р                 | MIPI-DSI data Lane 3 positive-end input pin         |

| 13            | GND     | Р                 | Ground                                              |

| 14            | D2N     | Р                 | MIPI-DSI data Lane negative-end input/output pin    |

| 15            | D2P     | Р                 | MIPI-DSI data Lane positive-end input pin           |

| 16            | GND     | Р                 | Ground                                              |

| 17            | CLKN    | Р                 | MIPI-DSI clock Lane negative-end input pin          |

| 18            | CLKP    | Р                 | MIPI-DSI clock Lane positive-end input pin          |

| 19            | GND     | Р                 | Ground                                              |

| 20            | D1N     | Р                 | MIPI-DSI data Lane 1 negative-end input/output pin  |

| 21            | D1P     | Р                 | MIPI-DSI data Lane1 positive-end input pin          |

| 22            | GND     | Р                 | Ground                                              |

| 23            | D0N     | Р                 | MIPI-DSI data Lane 0 negative-end input/output pin  |

| 24            | D0P     | Р                 | MIPI-DSI data Lane 0 positive-end input pin         |

| 25            | GND     | Р                 | Ground                                              |

| 26            | ID1(NC) | 1                 | Open                                                |

| 27            | RESET   | I                 | Chip reset signal("L"->Active)                      |

| 28            | NC      | 1                 | Open                                                |

| 29            | IOVCC   | Р                 | Supply voltage to the interface pins(+1.8V or 2.8V) |

| 30            | VCI     | Р                 | Supply voltage to the analog circuit (+2.8V)        |

| 31            | TPGND   | Р                 | Ground                                              |

| 32            | SCL     | I                 | Serial interface clock                              |

| 33            | SDA     | I/O               | Serial interface date                               |

| 34            | TPVDD   | Р                 | Power of CTP                                        |

| 35            | TPRST   | I                 | Reset low                                           |

| 36            | INT     | 0                 | State change interrupt                              |

| 37            | TPGND   | Р                 | Ground                                              |

| 38-40         | GND     | Р                 | Ground                                              |

ÓÚÙ€ÏÌŒFF€Œ P.8

# **8.AC CHARACTERISTICS**

# **8.1 MIPI-DSI characteristics**

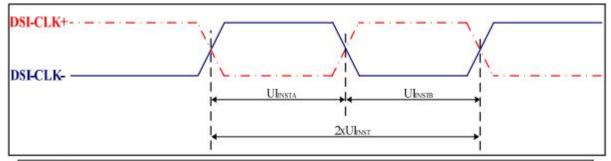

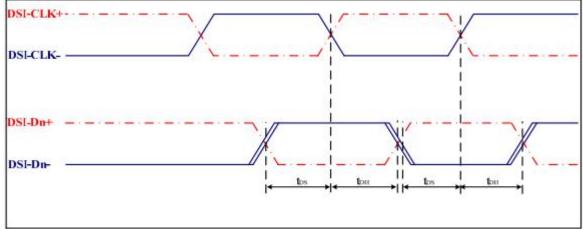

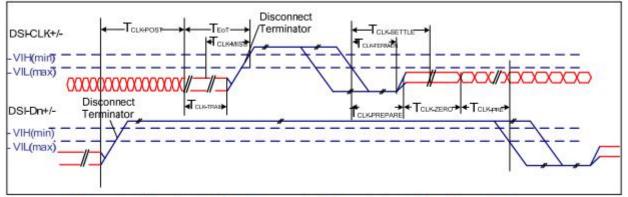

# 8.1.1 High speed mode

| Parameter Symbol |                |                                  | Sp   | ** ** |       |      |  |

|------------------|----------------|----------------------------------|------|-------|-------|------|--|

| Parameter        | Symbol         | Parameter                        | MIN  | TYP   | MAX   | Unit |  |

|                  |                | High Speed Mode                  |      |       |       |      |  |

| DSI-CLK+/-       | 2Xu linst      | Double UI instantaneous          | 2,22 | -     | 25    | ns   |  |

| DSI-CLK+/-       | UINSTA, UINSTB | UI instantaneous Halfs           | 1,11 | -     | 12.5  | ns   |  |

| DSI-Dn+/-        | Tds            | Data to clock setup time         | 0.15 | -     | -     | UI   |  |

| DSI-Dn+/-        | Tah            | Data to clock hold time          | 0.15 | 84    | 20    | UI   |  |

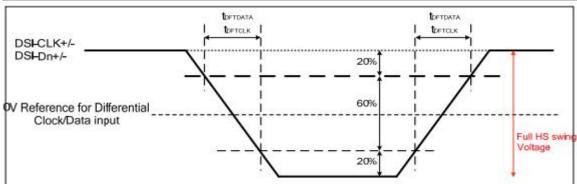

| DSI-CLK+/-       | Tdnclk         | Differential rise time for clock | 150  | -     | 0.3UI | ps   |  |

| DSI-Dn+/-        | Tdridata       | Differential rise time for data  | 150  |       | 0.3UI | ps   |  |

| DSI-CLK+/-       | Tdffclk        | Differential fall time for clock | 150  | -     | 0,3UI | ps   |  |

| DSI-Dn+/-        | Tdftdata       | Differential fall time for data  | 150  | 12    | 0.3UI | ps   |  |

Figure: AC characteristics for MIPI-DSI High speed mode

ÓÚÙ€Ï Ì ŒFF€Œ P. 9

# 8.1.2 Low power mode

| Parameter Symbo | Symbol     | Parameter                                                             | S       | Unit |         |     |

|-----------------|------------|-----------------------------------------------------------------------|---------|------|---------|-----|

| 1 ai ainetei    | Symbol     | Tatameter                                                             | MIN     | TYP  | MAX     | Cin |

|                 |            | Low Power Mode                                                        |         |      |         |     |

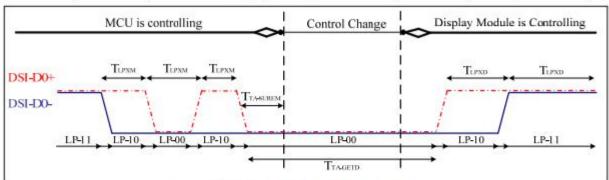

| DSI-D0+/-       | TLPXM      | Length of LP-00, LP-01, LP-10 or LP-11<br>periods MPU Display Module  | 50      | -    |         | ns  |

| DSI- D0+/-      | TLPXD      | Length of LP-00, LP-01, LP-10 or LP-11<br>periods Display Modulen MPU | 58      | -    | (S=)    | ns  |

| DSI- D0+/-      | TTA-SURED  | Time-out before the MPU start driving                                 | TLPXD   | -    | 2XTLPXD | ns  |

| DSI- D0+/-      | TTA-GETD   | Time to drive LP-00 by display module                                 | 5XTLPXD |      | 028     | ns  |

| DSI- D0+/-      | TTA-GOD    | Time to drive LP-00 after turnaround request –<br>MPU                 | 4XTLPXD | 26   | -       | ns  |

| DSI- D0+/-      | Ratio TLPX | Ratio of TLPXM / TLPXD between MCU and display module                 | 2/3     | -    | 3/2     |     |

Figure: BTA from the MCU to the Display Module

Figure: BTA from the Display Module to the MCU

QÚÙ€ÏÌŒFF€Œ P. 10

# **8.1.3 Bursts**

| Danamatan    | Combal                       | Damanatan                                                                                             | Specific                      | ation      |            | Unit |

|--------------|------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------|------------|------------|------|

| Parameter    | Symbol                       | Parameter                                                                                             | MIN                           | TYP        | MAX        | Uni  |

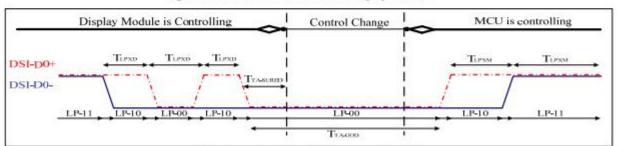

| ligh Speed l | Data Transmissi              | on Bursts                                                                                             |                               |            |            |      |

| DSI-Dn+/-    | TLPX                         | Length of any low-power<br>state period                                                               | 50                            | -          | -          | ns   |

| DSI- Dn+/-   | THS- PREPARE                 | Time to drive LP-00 to prepare for<br>HS transmission                                                 | 40ns+4UI                      | -          | 85ns+6UI   | ns   |

| DSI- Dn+/-   | THS-<br>PREPARE+THS-<br>ZERO | THS-PREPARE+time to drive HS-0<br>before the sync sequence                                            | 145ns+10UI                    | 145ns+10UI |            | ns   |

| DSI- Dn+/-   | TD-TERM- EN                  | Time to enable Data Lane<br>receiver line termination measured<br>from when Dn crosses VIL(max)       | Time for Dn to reach VTERM-EN |            | 35ns+4UI   | ns   |

| DSI- Dn+/-   | THS-SKIP                     | Time-out at RX to ignore transition<br>period of EoT                                                  | 40                            | 323        | 55ns+4UI   | ns   |

| DSI- Dn+/-   | THS-TRAIL                    | Time to drive flipped differential<br>state after last payload data bit of a<br>HS transmission burst | max (8UI, 60ns+4UI)           | •          | -          | ns   |

| DSI- Dn+/-   | THS-EXIT                     | Time to drive LP-11 after HS burst                                                                    | 100                           | 250        | -          | ns   |

| DSI- Dn+/-   | ТеоТ                         | Time from start of THS-TRAIL<br>period to start of LP-11 state                                        | 547                           | •          | 105ns+12UI | ns   |

Figure: High Speed Data Transmission Bursts

QÚÙ€ÏÌŒFF€Œ P. 11

| Danisation Similar Danisation |                            |                                                                                                                                 | Specification                       |     |                |      |

|-------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----|----------------|------|

| Parameter                     | Symbol                     | ool Parameter                                                                                                                   |                                     | TYP | MAX            | Unit |

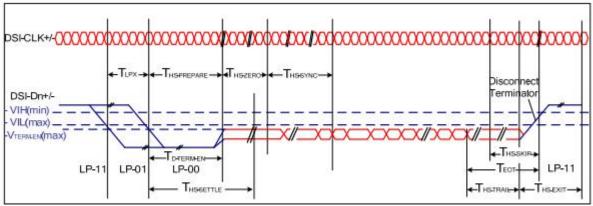

| Switching                     | the clock Lane b           | etween clock Transmission and Low Powe                                                                                          | er Mode                             |     |                | ×    |

| DSI-CLK+/-                    | TCLK-POST                  | Time that the transmitter shall continue sending<br>HS clock after the last associated Data Lane has<br>transitioned to LP mode | 60ns+52UI                           | -   | -              | ns   |

| DSI-CLK+/-                    | TCLK-PRE                   | Time that the HS clock shall be driven prior to<br>any associated Data Lane beginning the transition<br>from LP to HS mode      | 8                                   |     | -              | UI   |

| DSI-CLK+/-                    | TCLK-PREPARE               | Time to drive LP-00 to prepare for HS clock transmission                                                                        | 38                                  | 2   | 95             | ns   |

| DSI-CLK+/-                    | TCLK-TERM- EN              | Time to enable Clock Lane receiver line termination measured from when Dn crosses VIL(max)                                      | Time for Dn<br>to reach<br>VTERM-EN | -   | 38             | ns   |

| DSI- CLK+/-                   | TCLK-PREPARE<br>+TCLK-ZERO | TCLK-PREPARE + time for lead HS-0 drive<br>period before starting Clock                                                         | 300                                 | •   | -              | ns   |

| DSI- CLK+/-                   | TCLK-TRAIL                 | Time to drive HS differential state after last<br>payload clock bit of a HS transmission burst                                  | 60                                  | -   | 2              | ns   |

| DSI-CLK+/-                    | ТеоТ                       | Time from start of TCLK-TRAIL period to start of LP-11 state                                                                    | -                                   | 4   | 105ns+<br>12UI | ns   |

Figure: Switching the clock Lane between clock Transmission and Low Power Mode

ÚÚUĖ Ì ŒFF€Œ P. 12

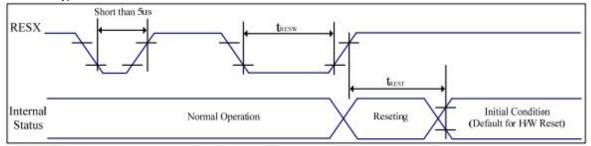

#### 8.2 Reset timing characteristics

VSS=0V, IOVCC=1.65V to 3.6V, VCI=2.5V to 6.0V, Ta = -30°C to 70°C

| Symbol            | Parameter                 | Related<br>Pins | MIN | TYP | MAX | Note                                        | Unit |

|-------------------|---------------------------|-----------------|-----|-----|-----|---------------------------------------------|------|

| $T_{\text{resw}}$ | *1) Reset low pulse width | RESX            | 10  | -   |     |                                             | us   |

|                   |                           |                 |     |     | 5   | When reset applied during<br>Sleep in mode  | ms   |

| Trest             | *2) Reset complete time   | .=              | -   | 5   | 120 | When reset applied<br>during Sleep out mode | ms   |

Table: Reset input timing

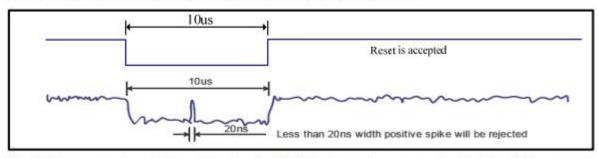

Note 1: Due to an electrostatic discharge on RESX line, spike does not cause irregular system reset according to the table below.

| RESX Pulse           | Action                                                          |

|----------------------|-----------------------------------------------------------------|

| Shorter than 5us     | Reset Rejected                                                  |

| Longer than 10us     | Reset                                                           |

| Between 5us and 10us | Reset starts (It depends on voltage and temperature condition.) |

Note 2: During the resetting period, the display will be blanked (The display is entering blanking sequence, which maximum time is 120ms, when Reset Starts in Sleep Out mode. The display remains the blank state in Sleep In mode), then return to default condition for H/W reset.

Note 3: During Reset Complete Time, ID1/ID2/ID3 and VCOM value in OTP will be latched to internal register. After a rising edge of RESX, there is a H/W reset complete time (Trest) which lasted 5ms. The loading operation will be done every time during this reset.

Note 4: Spike Rejection also applies during a valid reset pulse as shown below:

Note 5. It is necessary to wait 5msec after releasing RESX before sending commands. Also Sleep Out command cannot be sent for 120 msec.

ÓÚÙ€Ï Ì ŒFF€Œ P. 13

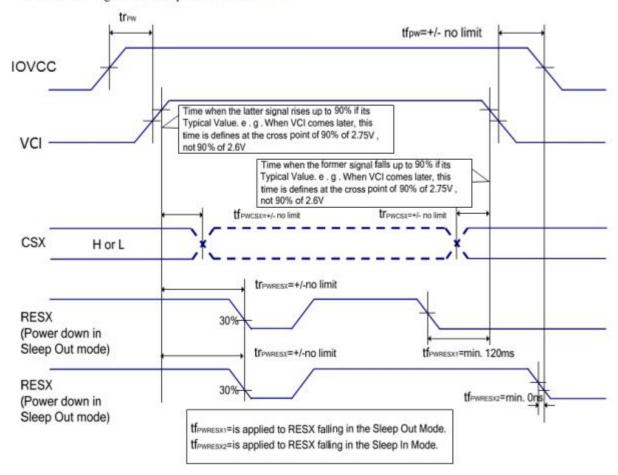

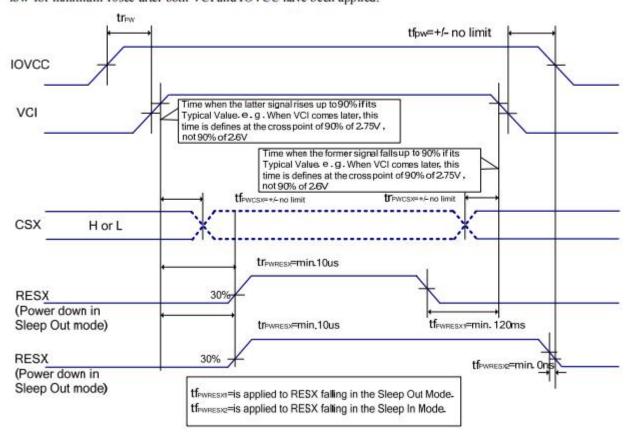

#### 9. POWER SEQUENCE

To prevent the device damage from latch up and Improve subjective display effect, the power ON/OFF sequence shown below must be followed.

IOVCC and VCI can be applied in any order. IOVCC and VCI can be powered down in any order.

During power off, if LCD is in the Sleep Out mode, VCI and IOVCC must be powered down minimum 120msec after RESX has been released.

During power off, if LCD is in the Sleep In mode, IOVCC or VCI can be powered down minimum 0msec after RESX has been released.

CSX can be applied at any timing or can be permanently grounded. RESX has priority over CSX.

Note 1: There will be no damage to the display module if the power sequences are not met.

Note 2: There will be no abnormal visible effects on the display panel during the Power On/Off Sequences.

Note 3: There will be no abnormal visible effects on the display between end of Power On Sequence and before receiving Sleep Out command.

Also between receiving Sleep In command and Power Off Sequence.

If RESX line is not held stable by host during Power On Sequence, then it will be necessary to apply a Hardware Reset (RESX) after Host Power On Sequence is complete to ensure correct operation. Otherwise function is not guaranteed.

The power on/off sequence is illustrated below:

#### Case 1 - RESX line is held high or unstable by host at power on

If RESX line is held High or unstable by the host during Power On, then a Hardware Reset must be applied after both VCI and IOVCC have been applied – otherwise correct functionality is not guaranteed. There is no timing restriction upon this hardware reset.

ΟÚÙ€ÏÌOŒF€Œ P. 14

### Case 2 - RESX line is held low or unstable by host at power on

If RESX line is held Low (and stable) by the host during Power On, then the RESX must be held low for minimum 10sec after both VCI and IOVCC have been applied.

#### **Uncontrolled power off**

The uncontrolled power off means a situation when e.g. there is removed a battery without the controlled power off sequence. There will not be any damages for the display module or the display module will not cause any damages for the host or lines of the interface.

At an uncontrolled power off the display will go blank and there will not be any visible effects within (TBD) second on the display (blank display) and remains blank until "Power On Sequence" powers it up.

ÓÚÙ€Ï Ì ŒFF€Œ P. 15

# 10. RELIABILITY TEST CONDITIONS

| No.  | Test item                           | Test condition                                            |                    | Inspection after test                                                |

|------|-------------------------------------|-----------------------------------------------------------|--------------------|----------------------------------------------------------------------|

| 10.1 | High temperature storage test       | +80°C/240 hours                                           |                    |                                                                      |

| 10.2 | Low temperature storage test        | -30°C/240 hours                                           |                    |                                                                      |

| 10.3 | High temperature operating test     | +70°C/120 hours                                           |                    |                                                                      |

| 10.4 | Low temperature operating test      | -20°C/120 hours                                           |                    | Inspection after                                                     |

| 10.5 | Temperature cycle storage test      | -30°C ~ 25°C ~ +80°<br>(30min.) (10min.) (30              | •                  | 2~4hours storage at room temperature, the sample shall be free       |

| 10.6 | High temperature high humidity test | +50°C*90% RH/120                                          | hours              | from defects :  1.Current changing                                   |

| 10.7 | Vibration test                      | Frequency : 250 r/mi<br>Amplitude : 1 inch<br>Time: 45min | in                 | value before test and after test is 50% larger; 2. Function defect : |

|      |                                     | Drop direction:<br>1 corner/3 edges/6 s                   | ides 10 times      | Non-display,abnormal-d isplay,missing lines, Short lines.ITO         |

|      |                                     | Packing weight(kg)                                        | Drop height(cm)    | corrosion;                                                           |

| 10.8 | Drop test                           | <11                                                       | 80±1.6             | 3.Visual defect : Air bubble in the LCD,Seal                         |

|      |                                     | 11≦G<21                                                   | 60±1.2             | leak,Glass crack.                                                    |

|      |                                     | 21 ≦ G<31                                                 | 21 ≦ G ⟨ 31 50±1.0 |                                                                      |

|      |                                     | 31 ≦ G<40 40±0.8                                          |                    |                                                                      |

| 10.9 | ESD test                            | Air discharge: ±8KV,<br>Contact discharge: ±              |                    |                                                                      |

#### Remark:

- 1. The test samples should be applied to only one test item.

- 2. Sample size for each test item is 3~5pcs.

- 3. For High temperature high humidity test, Pure water(Resistance>10M $\Omega$ ) should be used.

- 4.In case of malfunction defect caused by ESD damage, if it would be recovered to normal state after resetting, it would be judged as a good part.

- 5.B/L evaluation should be excepted from reliability test with humidity and temperature: Some defects such as black spot/blemish can happen by natural chemical reaction with humidity and Fluorescence B/L has.

- 6. Failure judgment criterion: Basic specification, Electrical characteristic, Mechanical characteristic, Optical characteristic.

- 7. After the reliability test, the product only guarantees operation, but don't guarantee all of the cosmetic specification.

QÚÙ€ÏÌŒFF€Œ P. 16

# 11.INSPECTION CRITERION

#### 11.1. Objective

The TFT test criterion are set to formalize TFT quality standards for GTK with reference to those of the customer for inspection, release and acceptance of finished TFT products in order to guarantee the quality of TFT products required by the customer.

#### 11.2. Scope

The criterion is applicable to all the TFT products manufactured by GTK.

### 11.3. Equipment for Inspection

Electrical tester, electrical testing machines, vernier calipers, microscopes, magnifiers, anti-static wrist straps, finger cots, labels, tri-phase cold and hot shock machine, constant temperature and humidity chamber, backlight table, ovens for high-low temperature experiments, refrigerators, constant voltage power supply (DC) )), desk Lamps, etc.

#### 11.4. Sampling Plan and Reference Standards

#### 11.4.1.1 Sampling plan:

Refer to National Standard GB/T 2828.1---2012/ISO2859-1:1999, level II of normal levels:

| Product<br>Category | Consumer<br>Electronics | Non-consumer<br>Electronics | Industrial      | Automobile      |

|---------------------|-------------------------|-----------------------------|-----------------|-----------------|

| AQL                 | MA=0.4 MI=1.5           | MA=0.4 MI=1.0               | MA=0.25 MI=0.65 | MA=0.15 MI=0.40 |

11.4.1.2 GB/T 2828.1---2012/ISO2859-1:1999 Sampling check procedure in count

11.4.1.3 GB/T 18910. Standard for LCM parts

11.4.1.4 GB/T24213-2008 Basic Environmental Test Procedures for Electrical and Electronic Products 11.4.1.5 IPC-A-610E Acceptability of Electronic Assemblies

### 11.5. Inspection Conditions and Inspection Reference

11.5.1Cosmetic inspection: shall be done normally at 23±5°C of the ambient temperature and 45~75% RH of relative humidity, under the ambient luminance between 500 lux~1000 lux and at the distance of 30cm apart between the inspector's eyes and the LCD panel and normally in reflected light. For backlight LCM, cosmetic inspection shall be done under the ambient luminance less than 100lux with the backlight on.

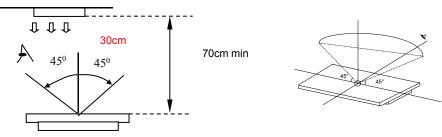

11.5.2 The TFT shall be tested at the angle of 45°left and right and 0-45° top and bottom as the following picture showing:

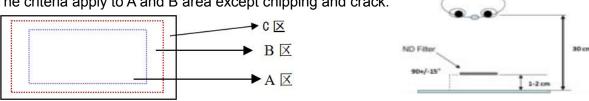

11.5.3 Definition of viewing area (VA)

A area: Active area (AA area) B area: Viewing area (VA area)

C area: Non-viewing area (not viewing after customer assembly)

If there is any appearance viewing defect which do not affect product quality and customer assembly in C area, it's accepted in generally.

The criteria apply to A and B area except chipping and crack.

οίι)⊭ïìο#F#OF P. 17

- 11.5.4 Inspection with naked eyes(exclusive of the inspection of the physical dimensions of defects carried out with magnifiers)

- 11.5.5 ND card use method(refer to right conner image ) and scope: Multi-bright dot; Mura(Black/Gray pattern uneven); dark line and so on.

- 11.5.6 Undefined items or other special items, refer to mutual agreement and limited sample. If criterion does not match product specifications/ technical requirement, both should be subject to special inspection criterion agreed by customer.

#### 11.6 Defects and Acceptance Standards

- 11.6.1 Electrical properties test

- 11.6.1.1 Test voltage(V): Refer to the instruction of testers and the product specification or drawing and the display content and parameters and display effects shall conform to the product specification and drawing.

- 11.6.1.2 Current Consumption(I): Refer to approved product specifications or drawings.

11.6.1.3 Function items(Defect category MA)

| No.         | Defects                          | Descriptions                                                                                                  | Pictures         | Inspection method/tools               | Defect<br>category |

|-------------|----------------------------------|---------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------|--------------------|

| 11.6.1.3.1  | No display<br>/reaction          | shows no picture/display in normal connected situation.                                                       |                  | Naked eyes/<br>testers                | MA                 |

| 11.6.1.3.2  | Missing segment                  | Shows missing lines in normal display                                                                         |                  | Naked eyes/<br>testers                | MA                 |

| 11.6.1.3.3  | Dark line                        | Only visible on gray pattern, 1 or more vertical/horizontal lines: 5%ND, not visible, OK                      | /                | Naked eyes/<br>testers                | MA                 |

| 11.6.1.3.4  | POL angle defect                 | Not accepted                                                                                                  | 正常<br>POL斯茲180麼后 | Naked eyes/<br>testers                | MA                 |

| 11.6.1.3.5  | Image<br>retention<br>(sticking) | Chess pattern stays for<br>30mins and change to 50%<br>gray pattern, disappear in 10s,<br>OK; if time>10s, NG |                  | Naked eyes/<br>testers                | MA                 |

| 11.6.1.3.6  | Flicker                          | Refer to Limit sample if<br>essential or flicker value<br><-30dB (measured by<br>CA310A); OK                  |                  | Naked eyes/<br>CA310A                 | MA                 |

| 11.6.1.3.7  | Display<br>abnormal              | Not accepted                                                                                                  |                  | Naked eyes/<br>testers                | MA                 |

| 11.6.1.3.8  | Cross-talk                       | Refer to limited sample                                                                                       | +                | Naked eyes/<br>limited sample         | MA                 |

| 11.6.1.3.9  | Display<br>dim/bright            | Refer to limited sample                                                                                       | /                | Naked eyes/<br>limited sample         | МА                 |

| 11.6.1.3.10 | Contrast                         | Refer to limited sample                                                                                       | 1                | Naked eyes/<br>limited sample         | MA                 |

| 11.6.1.3.11 | Huge<br>current                  | Out of spec, not accepted                                                                                     | /                | Ammeter                               | MA                 |

| 11.6.1.3.12 | TP function defect               | Not accepted                                                                                                  | 1                | Naked eyes/<br>Touch/<br>test program | MA                 |

QÚÙ€ÏÌŒF€Œ P. 18

#### 11.6.2 LCD dot/line defect

# 11.6.2.1 LCD pixel dot defect(defect category: MI)

| Item                            | Inspection criterion |         |          |              |  |  |  |

|---------------------------------|----------------------|---------|----------|--------------|--|--|--|

| Size                            | S <5"                | 5≤S<10" | 10≤S<15" | <u>S≥15"</u> |  |  |  |

| Color pixel dot defect(RGB dot) | 1                    | 2       | 2        | 3            |  |  |  |

| 2 connected bright dot          | 0                    | 1       | 1        | 1            |  |  |  |

| 3 connected bright dot or more  | 0                    | 0       | 1        | 0            |  |  |  |

| Bright dot quantity             | 1                    | 2       | 3        | 4            |  |  |  |

| Random dark dot quantity        | 2                    | 3       | 4        | <u>5</u>     |  |  |  |

| 2 connected dark dot            | 1                    | 1       | 2        | 2            |  |  |  |

| 3 connected dark dot or more    | 0                    | 0       | 0        | 0            |  |  |  |

| Dark dot quantity               | 3                    | 4       | 5        | <u>6</u>     |  |  |  |

| Multi-bright dot                | ND 5% hidden, O      | K       |          |              |  |  |  |

Remark: 2 bright dots distance DS≥15mm 2 dark dots distance DS≥5mm

- 1) Bright dot: Power on TFT and RGB dot in black display

- 2) Dark dot: Power on TFT and gray or black dot in RGB display

- 3) Multi-bright dot: Power on TFT and fluorescent tiny dot in black display(only visible in black display)

# 11.6.2.2 LCD appearance dot defect (defect category: MI)

|            |                                 | Inspectio              | n criterio                     | n               |                   |              |                           |               |               | Pict      | ure          | Inspection               |

|------------|---------------------------------|------------------------|--------------------------------|-----------------|-------------------|--------------|---------------------------|---------------|---------------|-----------|--------------|--------------------------|

| No.        | Item                            | Size                   | S <5"                          | 5≤S<1           | 10"               | 10≤S<br>15"  | <                         | <u>S≥1</u>    | <u> 5"</u>    |           |              | method/tool<br>s         |

|            |                                 | D≤0.15                 | ignore                         | ignore          | ;                 | D≤0.2;       |                           | <u>D≤0.2;</u> |               |           |              |                          |

|            |                                 | 0.15<<br>D≤0.25        | 3                              | 3               |                   | Not<br>count | t                         | ignore        |               | \$ b      |              | Naked eyes               |

|            | Dot defect                      | 0.25<<br>D≤0.30        | 1                              | 2               |                   | 0.2~0        | ).35                      | 0.2           | ~0.3 <u>5</u> | •         | a            | /film card<br>/magnifier |

| 11.6.2.2.1 | (black dot, white dot)          | 0.30<<br>D≤0.35        | 0                              | 1               |                   | Q'ty ≤       | ≦4                        | Q'ty          | <u>/ ≤ 5</u>  |           |              |                          |

|            | mile doty                       | 0.35<<br>D≤0.50        | 0                              | 0               |                   | 1            |                           | 2             |               |           |              |                          |

|            |                                 | D>0.5                  | 0                              | 0               |                   | 0            |                           | 0             |               |           |              |                          |

|            |                                 | Remark: [<br>Count dot |                                |                 |                   |              |                           |               |               |           |              | s multi-dot.             |

|            |                                 | Length<br>(mm)         | Width<br>(mm)                  | <u>S &lt;5"</u> | <u>5≤5</u><br>10" | <u> </u>     | <u>10≤5</u><br><u>15"</u> | <u> </u>      | <u>S≥15"</u>  |           |              |                          |

|            |                                 | Not count              | W≤0.03                         | Ignored         | Ign               | ored         | Igno                      | red           | Ignore        | <u>:d</u> |              |                          |

|            | : defect                        | L≤5                    | <u>0.03≤W</u><br>< <u>0.05</u> | 3               | 3                 |              | Igno                      | red           | Ignore        | <u>:d</u> | 1            | Naked<br>eyes            |

| 11.6.2.2.2 | Line defect<br>(visible<br>when | L≤5                    | <u>0.05≤W</u><br><0.08         | 0               | 1                 |              | 3                         |               | <u>3</u>      |           |              | /film card<br>/magnifier |

|            | power on)                       | L≤8                    | <u>0.05≤W</u><br><0.08         | 0               | 0                 |              | 1                         |               | 2             |           |              |                          |

|            |                                 | L>8                    | <u>W&gt;</u><br>0.08           | 0               | 0                 |              | 0                         |               | <u>0</u>      |           |              |                          |

|            |                                 |                        |                                | •               |                   | -            | •                         |               | •             |           |              | st light, show           |

|            |                                 | as watern<br>keeping s |                                | ıg/scratch      | bu'               | t can ı      | not be                    | e tou         | ıched, r      | 10 CC     | ontrol or re | efer to                  |

| 秋田微电子     |

|-----------|

| AVDISPLAY |

|            |                          | Size(mm                         | <u>S &lt;5"</u> | 5<9 < 10" | 10≤S<<br>15" | <u>S≥15"</u> |      |                          |

|------------|--------------------------|---------------------------------|-----------------|-----------|--------------|--------------|------|--------------------------|

|            | Dolorizon                | <u>D≤0.20</u>                   | Ignored         | Ignored   | Ignored      | Ignored      |      |                          |

| 11.6.2.2.3 | Polarizer convex-concave | <u>0.20&lt;</u><br><u>D≤0.5</u> | 2               | 2         | 3            | <u>5</u>     | \$ b | Naked eyes               |

|            | dot defect,<br>polarizer | <u>0.50&lt;</u><br><u>D≤0.8</u> | 0               | 1         | 2            | <u>3</u>     |      | /film card<br>/magnifier |

|            | bubble<br>defect         | <u>0.8&lt;</u><br><u>D≤1.5</u>  | 0               | 0         | 1            | 2            |      | 3                        |

|            |                          | <u>D&gt;</u><br>1.5mm           | 0               | 0         | 0            | <u>o</u>     |      |                          |

11.6.3 Chipping defect

| No.      | Item                                       | Accepted                            | d criterion(mm                                                                         | 1)                                                                               |                                         | MAJ | MIN |

|----------|--------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------|-----|-----|

|          | ITO conductive side                        | Х                                   | 1                                                                                      | ≤1/8L                                                                            | 1                                       |     |     |

| 11.6.3.1 | Z Z                                        | Υ                                   | Y≤1/6W                                                                                 | 1/6W<br><y≤1 4w<="" td=""><td>1/4W <y< td=""><td></td><td>1</td></y<></td></y≤1> | 1/4W <y< td=""><td></td><td>1</td></y<> |     | 1   |

|          | W N                                        | Accept                              | 2                                                                                      | 2                                                                                | 0                                       |     |     |

| 11.6.3.2 |                                            | X                                   | 1                                                                                      | ≤1/6L                                                                            | 1                                       |     |     |

| 11.0.3.2 | Corner chipping (ITOpins position)         | Υ                                   | Y≤1/2W                                                                                 | 1/2W <y≤w< td=""><td>W <y< td=""><td></td><td>\ </td></y<></td></y≤w<>           | W <y< td=""><td></td><td>\ </td></y<>   |     | \   |

|          |                                            | Accept                              | 2                                                                                      | 1                                                                                | 0                                       |     |     |

|          | Z ×                                        | as per 6.<br>into black<br>chipping | hipping occur<br>3.3; at the sar<br>torder of the<br>effect the elect<br>as per 6.3.1. | ld not enter<br>corner                                                           |                                         |     |     |

|          | Chipping in sealed area (outside chipping) | Х                                   | 1                                                                                      | ≤1/8L                                                                            | 1                                       |     |     |

|          | (outside chipping)                         | Y<br>(outside<br>chipping)          | Not enter                                                                              | Enter<br>Y≤H                                                                     | H <y< td=""><td></td><td></td></y<>     |     |     |

|          | X Y                                        | Y<br>(inside<br>chipping)           | sealant                                                                                | Enter<br>Y≤1/2H                                                                  | 1/2H <y< td=""><td></td><td></td></y<>  |     |     |

| 44.0.0.0 | 17 -                                       | Z                                   | ≤T                                                                                     | ≤1/2T                                                                            | 1                                       |     |     |

| 11.6.3.3 |                                            | Accept                              | 2                                                                                      | 1                                                                                | 0                                       |     | 1   |

|          | Chipping in sealed area (inside chipping)  | sealing a occurred                  | rea are same in the opposi                                                             | and outer chip<br>. When the chip<br>te of stage, Y a<br>onduction side s        | oping<br>s per the                      |     |     |

|          |                            |                         | / <u>////////////////////////////////////</u>     | L/-\Y                                                                                                           |                                                                        |  |           |

|----------|----------------------------|-------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--|-----------|

|          | conductive side            | X                       | 1                                                 | ≤1/6L                                                                                                           | 1                                                                      |  |           |

|          | (back side chipping        | Υ                       | Y≤1/3W                                            | 1/3W<br><y≤2 3w<="" td=""><td>2/3W <y< td=""><td></td><td><math>\sqrt{}</math></td></y<></td></y≤2>             | 2/3W <y< td=""><td></td><td><math>\sqrt{}</math></td></y<>             |  | $\sqrt{}$ |

| 11.6.3.4 | Z                          | Accept                  | 2                                                 | 2                                                                                                               | 0                                                                      |  |           |

|          |                            | Chipping int            | to ITO side ,re                                   | efer to 6.3.1                                                                                                   |                                                                        |  |           |

|          | Protruding LCD             | X                       | 1                                                 | ≤1/8L                                                                                                           | 1                                                                      |  |           |

|          | poor cutting and LCD burrs | Υ                       | ≤1/6W                                             | 1/6W<br><y≤1 5w<="" td=""><td>1/5W <y< td=""><td rowspan="2"></td><td><math>\sqrt{}</math></td></y<></td></y≤1> | 1/5W <y< td=""><td rowspan="2"></td><td><math>\sqrt{}</math></td></y<> |  | $\sqrt{}$ |

| 11.6.3.5 |                            | Z                       | 1                                                 | /                                                                                                               | 1                                                                      |  | •         |

|          | W. W.                      | Accept                  | 1                                                 | 1                                                                                                               | 1                                                                      |  |           |

|          |                            | the outside of drawing. | protruding co                                     | ntrol as per th                                                                                                 | e tolerance                                                            |  |           |

| 11.6.3.6 | Crack                      | crack expar             | occur cracks<br>nd to inside is<br>as per the dar | NG, but to ou                                                                                                   | itside is OK                                                           |  | V         |

Remark:1)X means the length of chipping; Y means the width; Z means the thickness; W means the step width of the two glasses; H means the distance from the glass edge to the seal inner edge; t means glass thickness.

11.6.4 Backlight components

| No.      | Item                     | Description                                                                                                                                                                                                 | Accepted criterion           | MAJ | MIN      |

|----------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----|----------|

| 11.6.4.1 | No backlight wrong Color | 1                                                                                                                                                                                                           | Rejected                     | √   |          |

| 11.6.4.2 | Color<br>deviation       | When powered on, the LCD color differs from its sample and found that the color not conforming to the drawing after testing.                                                                                | Refer to sample and drawing. |     | 1        |

| 11.6.4.3 | Brightness<br>deviation  | When powered on, the LCD brightness differs from its sample and is found after testing not conforming to the drawing; or if it conforms to the drawing but the brightness over ±40% than its typical value. | Refer to sample and drawing. |     | <b>V</b> |

| 11.6.4.4 | Uneven<br>brightness     | Uneven on the same LCD and out of the specification of the drawing. The no specification evenness= (the max value-the min value)/ mean value< 70%.                                                          | Refer to sample and drawing. |     | <b>√</b> |

| 11.6.4.5 | Spot/line<br>/scratch    | When power on, it has dirty spot, scratches and so on spot and line defects.                                                                                                                                | Refer to 6.2.2               |     | 1        |

# 11.6.5 Metal frame (Metal Bezel)

| No.      | Item                                                | Description                                                                                                                                                             | Accepted criterion | MAJ      | MIN      |

|----------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------|----------|

| 11.6.5.1 | Material & surface treatment                        | Metal frame/surface treatment do not conform to the specifications.                                                                                                     | Rejected           | <b>V</b> |          |

| 11.6.5.2 | Tab twist<br>Unconformity/<br>Tab not twisted       | Wrong twist method or direction and twist tabs are not twisted as required.                                                                                             | Rejected           | <b>V</b> |          |

| 11.6.5.3 | Bezel paint loss                                    | 1.Front surface: Paint peel off and scratch to the                                                                                                                      |                    |          | <b>V</b> |

| 11.6.5.4 | Bezel scratch                                       | bottom Dot:D≤0.5mm, exceeds 3; Line:L≤3.0mm,W≤0.05mm                                                                                                                    |                    |          | <b>V</b> |

| 11.6.5.5 | Painting peel off, discoloration, dent, and scratch | exceeds 2;<br>2.Front dent, air bubble and side<br>with paint peeling off scratch to the<br>bottom<br>Dot: D≤1.0mm, exceeds 3;<br>Line:L≤10.0mm,W≤0.05mm,<br>exceeds 2; | Rejected           |          | <b>V</b> |

| 11.6.5.6 | Burr                                                | Burr(s) on metal bezel is so long as to get into viewing area.                                                                                                          | Rejected           |          | <b>V</b> |

# 11.6.6 FPC

| No.      | Item                     | Description                                                                                                                                             | Accepted criterion                                                                                                                                            | MAJ      | MIN      |

|----------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|

| 11.6.6.1 | Model & P/N              | Material model & P/N                                                                                                                                    | Keep the same with drawing and technical requirement                                                                                                          | <b>V</b> |          |

| 11.6.6.2 | Dimension/<br>position   | Dimension in drawing spec  f w H X Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y                                                                                  | f≤1/3w, h≤1/3H, dimension in drawing spec-> OK Conducive material and ITO/PDA connective area must over than 1/2. Entire dimension must be in spec tolerance. |          | √        |

| 11.6.6.3 | FPC appearance           | Hot pressing material get<br>broken, folding line open;<br>FPC golden finger oxidate,<br>broken ,scratch ,foreign<br>material which cause line<br>short | Broken length<2mm; FPC line is OK- > Accepted Crack and line broken-> Rejected                                                                                |          | <b>√</b> |

| 11.6.6.4 | FPC burr                 | Burr near FPC edge area                                                                                                                                 | When cover line and burr length ≤1.0mm->Accepted                                                                                                              |          | √        |

| 11.6.6.5 | FPC falling off          | FPC bonding area falling off; silica gel breaking                                                                                                       | Rejected                                                                                                                                                      |          | √        |

| 11.6.6.6 | Sealant missing ITO line | Sealant is not covered all ITO line                                                                                                                     | Rejected                                                                                                                                                      | <b>V</b> |          |

| 11.6.6.7 | Missing sealant          | No sealant                                                                                                                                              | Rejected                                                                                                                                                      | <b>V</b> |          |

| 11.6.6.8 | Sealant                  | Sealant height > product total height                                                                                                                   | Rejected                                                                                                                                                      | <b>V</b> |          |

# 11.6.7 SMT

| No.      | Item                      | Description                                                                                               | Accepted criterion | MAJ      | MIN      |

|----------|---------------------------|-----------------------------------------------------------------------------------------------------------|--------------------|----------|----------|

| 11.6.7.1 | Soldering<br>bridge       | Solder between adjacent pads and components                                                               | Rejected           |          | <b>√</b> |

| 11.6.7.2 | Solder<br>ball/splash     | Solder ball/tin dross causing short circuit at the solder point. There are active solder ball and splash. | Rejected           |          | <b>V</b> |

| 11.6.7.3 | Soldering excursion       | Soldering slant > 1/3 soldering pad  「學盘宽度」  「學養宽度」                                                       | Rejected           |          | <b>1</b> |

| 11.6.7.4 | Component wrong attaching | Component on PCB differs with drawing: wrong one, extra one, lack one, opposite polarity                  | Rejected           | √        |          |

|          | wrong attaching           | JUMP short circuit on PCB: extra soldering ,lack soldering.                                               | Rejected           | √        |          |

| 11.6.7.5 | Component falling off     | Soldering but component is missing                                                                        | Rejected           | <b>√</b> |          |

| 11.6.7.6 | Wrong component           | Component model/spec differs from product specification                                                   | Rejected           | <b>√</b> |          |

# 11.6.8 General Appearance

| No.      | Item                      | Description                                                                       | Accepted criterion                                       | MAJ      | MIN      |

|----------|---------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------|----------|----------|

| 11.6.8.1 | Dimension                 | According to drawing                                                              | Accepted                                                 | √        |          |

| 11.6.8.2 | Surface stain             | Defect mark or label are not removed residual glue, and finger print,etc;         | Rejected                                                 |          | V        |

| 11.6.8.3 | Assembly foreign material | Dot/linear stain after assembly backlight and diffuse film TP assembly fogy stain | Invisible when power on->OK Refer to 6.2.2 dot/line spec |          | 1        |

| 11.6.8.4 | Mixture                   | Different model product in the same shipment                                      | Rejected                                                 | <b>√</b> |          |

| 11.6.8.5 | Product mark              | Missing, unclear, incorrect, or misplaced part                                    | Rejected                                                 |          | <b>V</b> |

| 11.6.8.6 | Component mark            | Silk screen mark clear, resistance measured value in spec                         | Accepted (Refer to customer special requirement          |          | <b>\</b> |

| 11.6.8.7 | Newton's rings            | Area<1/6 screen area quantity≤1                                                   | Accepted                                                 |          | <b>√</b> |

|           |            | /-\V   )   S  = L/-\Y                                                                                                                                                     |                                   |           |

|-----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------|

| 11.6.8.8  | Mura       | 1.In black display ND 5% invisible ->OK; visible->NG 2.Naked eyes inspection RGB display invisible Black display, area<1/4 screen area                                    | Refer to limited sample           | √         |

| 11.6.8.9  | Light leak | 1.LCD edge(near backlight) shadow<br>by LCD lamps irregular illuminate<br>2.Judge in black/white/gray display<br>(slight leaky is yellowish, greenish,<br>bluefish ->NG); | Refer to limited sample Tape 浮起漏光 | <b>√</b>  |

| 11.6.8.10 | Polarizer  | 1.Polarizer slant.Cover VA and not over LCD edge     2.No unmovable stain or finger print in polarizer VA     3.Bubble/warped but not enter VA                            | Accepted                          | <b>√</b>  |

| 11.6.8.11 | TP defect  | 1.TP crack 2.TP stain(fogy&unremovable) 3.TP glue overflow to VA                                                                                                          | Rejected                          | $\sqrt{}$ |

Remark: Anything which is not clearly defined in 6.5~6.8 should refer to IPC-A-610E.Consumer Electronics, Non-consumer Electronics refer to class 1 and Industrial, Automobile refer to Class 2.

#### 11.7. Others

Items not specified in this document or released on compromise should be inspected with reference to mutual agreement and limit samples.

#### 12. HANDLING PRECAUTIONS

#### 12.1 Mounting method

The LCD module consists of two thin glass plates with polarizes which easily be damaged. And since the module in so constructed as to be fixed by utilizing fitting holes in the printed circuit board.

Extreme care should be needed when handling the LCD modules.

#### 12.2 Caution of LCD handling and cleaning

When cleaning the display surface, Use soft cloth with solvent [recommended below] and wipe lightly:

- .lsopropyl alcohol

- Ethyl alcohol

Do not wipe the display surface with dry or hard materials that will damage the polarizer surface.

Do not use the following solvent :

- .Water

- Aromatics

Do not wipe ITO pad area with the dry or hard materials that will damage the ITO patterns Do not use the following solvent on the pad or prevent it from being contaminated:

- Soldering flux

- •.Chlorine (CI), Sulfur (S)

If goods were sent without being silicon coated on the pad, ITO patterns could be damaged due to the corrosion as time goes on.

If ITO corrosion happen by miss-handling or using some materials such as Chlorine (CI), Sulfur (S) from customer, Responsibility is on customer.

# 12.3 Caution against static charge

The LCD module use C-MOS LSI drivers, so we recommended that you:

Connect any unused input terminal to Vdd or Vss, do not input any signals before power is turned on, and

ground your body, work/assembly areas, assembly equipment to protect against static electricity.

#### 12.4 Packing

Module employ LCD elements and must be treated as such.

- Avoid intense shock and falls from a height.

- •. To prevent modules from degradation, do not operate or store them exposed direct to sunshine or high temperature/humidity.

### 12.5 Caution for operation

- •.It is an indispensable condition to drive LCD's within the specified voltage limit since the higher voltage then the limit cause the shorter LCD life.

- •.An electrochemical reaction due to direct current causes LCD's undesirable deterioration, so that the use of direct current drive should be avoided.

- •.Response time will be extremely delayed at lower temperature then the operating temperature range and on the other hand at higher temperature LCD's how dark color in them. However those phenomena do not mean malfunction or out of order with LCD's, which will come back in the specified operation temperature.

- •.If the display area is pushed hard during operation, some font will be abnormally displayed but it resumes normal condition after turning off once.

- A slight dew depositing on terminals is a cause for electro-chemical reaction resulting in terminal open circuit

- •. Usage under the maximum operating temperature, 50%Rh or less is required.

- •. When fixed patterns are displayed for a long time, remnant image is likely to occur.

#### 12.6 Storage

In the case of storing for a long period of time for instance, for years for the purpose or replacement use, the following ways are recommended.

- •. Storing in an ambient temperature 10°C to 30°C, and in a relative humidity of 45% to 75%. Don't expose to sunlight or fluorescent light.

- •.Storing in a polyethylene bag with the opening sealed so as not to enter fresh air outside in it . And with no desiccant.

- •.Placing in a dark place where neither exposure to direct sunlight nor light's keeping the storage temperature range.

- .Storing with no touch on polarizer surface by the anything else.

It is recommended to store them as they have been contained in the inner container at the time of delivery from us.

#### 12.7 Safety

- •.It is recommendable to crash damaged or unnecessary LCD's into pieces and wash off liquid crystal by either of solvents such as acetone and ethanol, which should be burned up later.

- •. When any liquid leaked out of a damaged glass cell comes in contact with your hands, please wash it off well with soap and water.

#### 13. PRECAUTION FOR USE

- **13.1** A limit sample should be provided by the both parties on an occasion when the both parties agreed its necessity. Judgment by a limit sample shall take effect after the limit sample has been established and confirmed by the both parties.

- **13.2** On the following occasions, the handing of problem should be decided through discussion and agreement between responsible of the both parties.

- When a question is arisen in this specification.

- •. When a new problem is arisen which is not specified in this specifications.

- •.When an inspection specifications change or operating condition change in customer is reported to GTK, and some problem is arisen in this specification due to the change.

- •. When a new problem is arisen at the customer's operating set for sample evaluation in the customer site.

#### 14. PACKING SPECIFICATION

Please consult our technical department for detail information.

# 15. INITIALIZATION CODE

```

#define VBPD

8

#define VFPD

8

#define VSPW

2

#define HBPD

30

#define HFPD

24

#define HSPW

#define HDP

400

#define VDP

1280

Wrt_Reg_3051(0xFF,0x30);

Wrt Reg 3051(0xFF,0x52);

Wrt Reg 3051(0xFF,0x01);

Wrt Reg 3051(0xE3,0x00);

Wrt Reg 3051(0xF6,0xC0);

Wrt Reg 3051(0xF0,0x00);

Wrt_Reg_3051(0x24,0x08);

Wrt_Reg_3051(0x25,0x0A);

Wrt Reg 3051(0x28,0xb4);

Wrt Reg 3051(0x29,0x44);

Wrt Reg 3051(0x2a,0xff);

Wrt Reg 3051(0x37,0x74);

Wrt Reg 3051(0x38,0x7f);

Wrt_Reg_3051(0x39,0x2C);

Wrt_Reg_3051(0x40,0x0E);

Wrt Reg 3051(0x49,0x3C);

Wrt_Reg_3051(0x59,0xfe);

Wrt Reg 3051(0x5C,0x00);

Wrt Reg 3051(0x6D,0x00);

Wrt Reg 3051(0x6E,0x00);

Wrt Reg 3051(0x80,0x20);

Wrt Reg 3051(0x91,0x77);

Wrt Reg 3051(0x92,0x77);

Wrt_Reg_3051(0x99,0x54);

Wrt_Reg_3051(0x9B,0x56);

Wrt_Reg_3051(0xA0,0x55);

Wrt Reg 3051(0xA1,0x50);

Wrt Reg 3051(0xA4,0x9C);

Wrt Reg 3051(0xA7,0x02);

Wrt Reg 3051(0xA8,0x01);

Wrt Reg 3051(0xA9,0x21);

Wrt Reg 3051(0xAA,0xA8);

Wrt_Reg_3051(0xAB,0x28);

Wrt_Reg_3051(0xAC,0xE0);

Wrt Reg 3051(0xAD,0xE2);

Wrt Reg 3051(0xAE,0xE2);

Wrt Reg 3051(0xAF,0x02);

Wrt Reg 3051(0xB0,0xE2);

Wrt Reg 3051(0xB1,0x26);

Wrt Reg 3051(0xB2,0x28);

Wrt Reg 3051(0xB3,0x28);

Wrt_Reg_3051(0xB4,0x22);

```