# SPECIFICATION FOR TFT MODULE

**MODULE NO.: IPS040A101A**

**CUST OMER NO.:**

Rev No.: O

| GTK       | PREPARED BY       | CHECKED BY | APPROVED BY |

|-----------|-------------------|------------|-------------|

| SIGNATURE | A B P             | 43         | Nota Liu    |

| DATE      | 2019.02.14 2019.0 | 2.14       | 2019.02.14  |

|                      | SIGNATURE DATE |  |

|----------------------|----------------|--|

| CUSTOMER<br>APPROVAL |                |  |

#### Notes:

- 1. Please contact GTK before assigning your product based on this module specification.

- 2. To improve the quality of product, and this product specification is subject to change without any notice.

## **REVISION RECORD**

| Rev No. | Rev date   | Contents      | Remarks     |

|---------|------------|---------------|-------------|

| 0       | 2019-02-14 | First release | Preliminary |

|         |            |               |             |

|         |            |               |             |

|         |            |               |             |

|         |            |               |             |

|         |            |               |             |

|         |            |               |             |

|         |            |               |             |

|         |            |               |             |

|         |            |               |             |

|         |            |               |             |

|         |            |               |             |

|         |            |               |             |

|         |            |               |             |

|         |            |               |             |

|         |            |               |             |

|         |            |               |             |

|         |            |               |             |

|         |            |               |             |

|         |            |               |             |

|         |            |               |             |

|         |            |               |             |

|         |            |               |             |

|         |            |               |             |

|         |            |               |             |

|         |            |               |             |

## CONTENTS

| 1. GENERAL INFORMATION              |

|-------------------------------------|

| 2. ABSOLUTE MAXIMUM RATINGS         |

| 3. ELECTRICAL CHARACTERISTICS4      |

| 4. BACKLIGHT CHARACTERISTICS4       |

| 5. EXTERNAL DIMENSIONS              |

| 6. ELECTRO-OPTICAL CHARACTERISTICS6 |

| 7. INTERFACE DESCRIPTION            |

| 8.AC CHARACTERISTICS                |

| 9. POWER SEQUENCE                   |

| 10. RELIABILITY TEST CONDITIONS     |

| 11.INSPECTION CRITERION             |

| 12. HANDLING PRECAUTIONS18          |

| 13. PRECAUTION FOR USE              |

| 14. PACKING SPECIFICATION19         |

| 15 INITIALIZATION CODE              |

## 1. GENERAL INFORMATION

| No. | Item                           | Contents              | Unit |

|-----|--------------------------------|-----------------------|------|

| 1   | LCD size                       | 4.0 inch (Diagonal)   | /    |

| 2   | Display mode                   | IPS/NORMALLY BLACK    | /    |

| 3   | Viewing direction(eye)         | FREE                  | /    |

| 4   | Gray scale inversion direction | -                     | /    |

| 5   | Resolution(H*V)                | 480 *480 Pixels       | /    |

| 6   | Module size (L*W*H)            | 76.00*78.20*2.30      | mm   |

| 7   | Active area (L*W)              | 71.856*70.176         | mm   |

| 8   | Pixel pitch (L*W)              | 0.135*0.135           | mm   |

| 9   | Interface type                 | RGB 24bit interface   | /    |

| 10  | Color Depth                    | 16.7M                 | /    |

| 11  | Module power consumption       | TBD                   | W    |

| 12  | Back light type                | EDGE,WHITE            | /    |

| 13  | Driver IC                      | ST7701S OR COMPATIBLE | /    |

| 14  | Weight                         | TBD                   | g    |

#### 2. ABSOLUTE MAXIMUM RATINGS

| Item                               | Symbol | Min. | Max. | Unit | Note  |  |  |  |  |

|------------------------------------|--------|------|------|------|-------|--|--|--|--|

| Power supply input voltage for TFT | VDD    | -0.3 | 4.6  | V    |       |  |  |  |  |

| Backlight current (normal temp.)   | ILED   | -    | 75   | mA   |       |  |  |  |  |

| Operation temperature              | Тор    | -20  | +70  | °C   | Note1 |  |  |  |  |

| Storage temperature                | Tst    | -30  | +80  | °C   | Note1 |  |  |  |  |

| Humidity                           | RH     | -    |      | RH   | Note1 |  |  |  |  |

#### Note1:

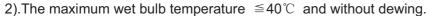

1). The relative humidity and temperature range are as below sketch, 90% RH Max.

## 3. ELECTRICAL CHARACTERISTICS

DC CHARACTERISTICS(at Ta=25°C)

| Item                                   | Symbol | Min.     | Тур. | Max.     | Unit | Note  |

|----------------------------------------|--------|----------|------|----------|------|-------|

| Power supply input voltage             | VDD    | 3.0      | 3.3  | 3.6      | V    |       |

| I/O logic voltage                      | VDDIO  | -        | -    | -        | V    |       |

| Input voltage 'H' level                | VIH    | 0.7VDDIO | -    | VDDIO    | V    |       |

| Input voltage 'L' level                | VIL    | VSS      | -    | 0.3VDDIO | V    |       |

| Power supply current                   | IVDD   | -        | 1    | -        | mA   |       |

| TFT gate on voltage                    | VGH    | -        | ı    | -        | V    |       |

| TFT gate off voltage                   | VGL    | -        | -    | -        | V    |       |

| Analog power supply voltage            | AVDD   | -        | -    | -        | V    |       |

| Differential input common mode voltage | Vcom   | -        | -    | -        | V    | Note1 |

Note1: The value is just the reference value. The customer can optimize the setting value by the different D-IC Vcom must be adjusted to optimize display quality, as Crosstalk and Contrast Ratio etc..

## 4. BACKLIGHT CHARACTERISTICS

(at Ta=25°C,RH=60%)

| Item                  | Symbol | Min.     | Тур.         | Max.  | Unit | Note      |

|-----------------------|--------|----------|--------------|-------|------|-----------|

| LED forward voltage   | VF     | 8.1      | 9.0          | 9.9   | V    | IF=20*3mA |

| LED forward current   | IF     | -        | 60           | -     | mA   |           |

| LED power consumption | PLED   | -        | 0.54         | -     | W    | Note1     |

| Number of LED         | -      |          | 9            |       | PCS  |           |

| Connection mode       | -      | 3 in ser | ies 3 in par | allel | /    |           |

| LED life-time         | -      | 20000    | -            | -     | Hrs  | Note2     |

Note1 : Calculator value for reference : IF\*VF = PLED

Note2: The LED life-time define as the estimated time to 50% degradation of initial brightness at Ta=25°C and IF =40mA. The LED lifetime could be decreased if operating IF is larger than 40mA.

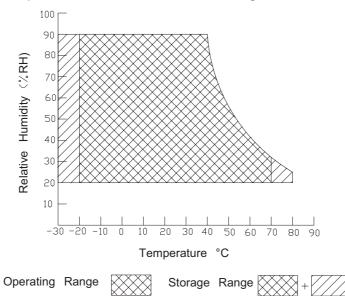

## 5. EXTERNAL DIMENSIONS

#### 6. ELECTRO-OPTICAL CHARACTERISTICS

| Item                 | Symbol  | Condition       | Min.  | Тур. | Max.  | Unit              | Remark  | Note   |

|----------------------|---------|-----------------|-------|------|-------|-------------------|---------|--------|

| Response time        | Tr+ Tf  |                 | -     | 25   | 35    | ms                | FIG.1   | Note 1 |

| Contrast ratio       | Cr      | -               | 640   | 800  | -     | -                 | FIG.2   | Note 2 |

| Surface<br>luminance | Lv      | θ=0°            | 250   | 300  | -     | cd/m <sup>2</sup> | FIG.2   | Note 3 |

| Luminance uniformity | Yu      | θ=0°            | 75    | 80   | -     | %                 | FIG.2   | Note 4 |

| NTSC                 | -       | θ=0°            | 1     | 50   | -     | %                 | FIG.2   | Note 5 |

|                      |         | ∅=90°           | 70    | 80   | -     | deg               | FIG.3   |        |

| Viouing angle        |         | ∅=270°          | 70    | 80   | -     | deg               | FIG.3   | Noto 6 |

| Viewing angle        | θ       | ∅=0°            | 70    | 80   | -     | deg               | FIG.3   | Note 6 |

|                      |         | ∅=180°          | 70    | 80   | -     | deg               | FIG.3   |        |

|                      | Red x   |                 |       | TBD  |       | -                 |         |        |

|                      | Red y   |                 |       | TBD  |       | -                 |         |        |

|                      | Green x | 0.00            |       | TBD  |       | -                 |         |        |

| CIE (x,y)            | Green y | θ=0°<br>∅=0°    | Тур   | TBD  | Тур   | -                 | FIG.2   | Note E |

| chromaticity         | Blue x  | v =0<br>Ta=25°C | -0.04 | TBD  | +0.04 | -                 | CIE1931 | Note 5 |

|                      | Blue y  | 10-20 0         |       | TBD  |       | -                 |         |        |

|                      | White x |                 |       | TBD  |       | -                 |         |        |

|                      | White y |                 |       | TBD  |       | -                 |         |        |

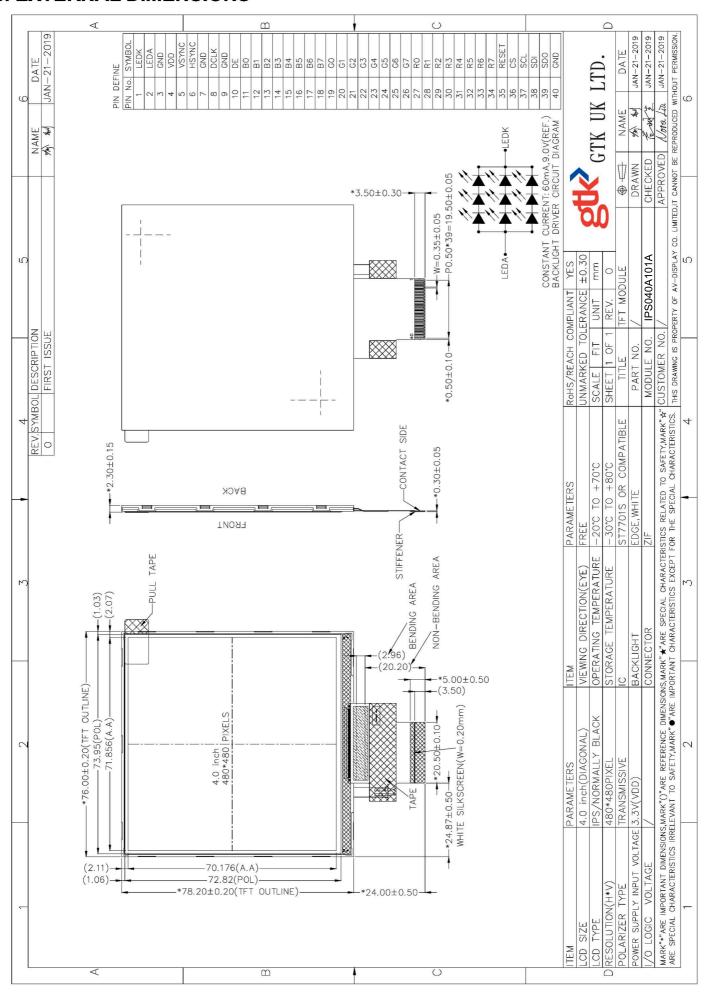

#### Note1. Definition of response time

The response time is defined as the LCD optical switching time interval between "White" state and "Black" state. Rise time  $(T_{ON})$  is the time between photo detector output intensity changed from 90% to 10%. And fall time  $(T_{OFF})$  is the time between photo detector output intensity changed from 10% to 90%. For additional information see FIG1.

#### Note2. Definition of contrast ratio

Contrast ratio(Cr) is defined mathematically by the following formula.

For more information see FIG.2.

Contrast ratio= Luminance measured when LCD on the "White" state

Luminance measured when LCD on the "Black" state

Measured at the center area of the LCD

#### Note3.Definition of surface luminance

Surface luminance is the luminance with all pixels displaying white.

For more information see FIG.2.

Lv = Average Surface Luminance with all white pixels(P1,P2,P3, .....,Pn)

#### Note4. Definition of luminance uniformity

The luminance uniformity in surface luminance is determined by measuring luminance at each test position 1 through n, and then dividing the maximum luminance of n points luminance by minimum luminance of n points luminance. For more information see FIG.2.

Yu = Minimum surface luminance with all white pixels (P1,P2,P3,.....,Pn)

Maximum surface luminance with all white pixels (P1,P2,P3,.....,Pn)

#### Note5. Definition of color chromaticity (CIE1931)

CIE (x,y) chromaticity, The x,y value is determined by screen active area center position P5. For more information see FIG.2.

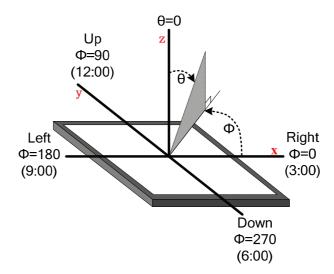

#### Note6. Definition of viewing angle

Viewing angle is the angle at which the contrast ratio is greater than 10. angles are determined for the horizontal or x axis and the vertical or y axis with respect to the z axis which is normal to the LCD surface. For more information see FIG.3.

For viewing angle and response time testing, the testing data is base on Autronic-Melchers's ConoScope or DMS series Instruments or compatible. For contrast ratio, Surface Luminance, Luminance uniformity and CIE, the testing data is base on TOPCON's BM-5or BM-7 photo detector or compatible.

#### FIG.1. The definition of response Time

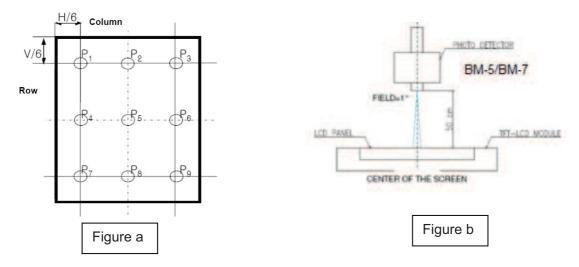

FIG.2. Measuring method for contrast ratio, surface luminance, luminance uniformity, CIE (x,y) chromaticity

H,V: Active area

Light spot size  $\varnothing$ =5mm(BM-5) or  $\varnothing$ =7.7mm (BM-7)50cm distance or compatible distance from the LCM surface to detector lens.

Test spot position : see Figure a.

measurement instrument: TOPCON's luminance meter BM-5 or BM-7 or compatible, see Figure b.

FIG.3. The definition of viewing angle

## 7. INTERFACE DESCRIPTION

**Module Interface description**

| Interface No. | Name       | I/O or connect to | Description                                        |

|---------------|------------|-------------------|----------------------------------------------------|

| 1             | LEDK       | Р                 | Power for LED backlight(Cathode)                   |

| 2             | LEDA       | Р                 | Power for LED backlight(Anode)                     |

| 3             | GND        | Р                 | Ground                                             |

| 4             | VDD        | Р                 | Power for LCD                                      |

| 5             | VSYNC      | I                 | Vertical sync input                                |

| 6             | HSYNC      | I                 | Horizontal sync input.                             |

| 7             | GND        | Р                 | Ground                                             |

| 8             | DCLK       | I                 | Dot clock                                          |

| 9             | GND        | Р                 | Ground                                             |

| 10            | DE         | I                 | Data enable                                        |

| 11-18         | Blue(0-7)  | I                 | Blue data                                          |

| 19-26         | Green(0-7) | I                 | Green data                                         |

| 27-34         | Red(0-7)   | I                 | Red data                                           |

| 35            | RESET      | I                 | Global reset pin                                   |

| 36            | CS         | I                 | Chip select input pin                              |

| 37            | SCL        | I                 | SCL: Serial clock input for SPI interface.         |

| 38            | SDI        | I                 | Serial data input I pin used for SPI Interface.    |

| 39            | SDO        | 0                 | Serial data output pin used for the SPI Interface. |

| 40            | GND        | Р                 | Ground                                             |

## **8.AC CHARACTERISTICS**

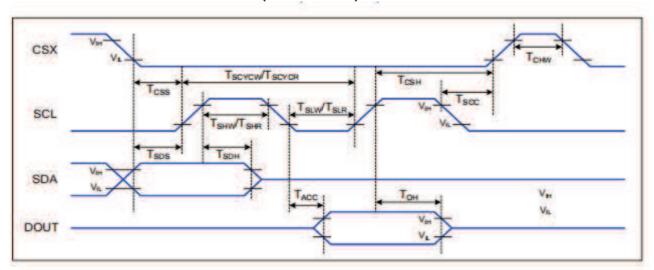

## 8.1 Serial Interface Characteristics (3-line serial):

Figure 1 3-line serial Interface Timing Characteristics

VDDI=1.8,VDD=2.8, AGND=DGND=0V, Ta=25℃

| Signal | Symbol             | Parameter                      | Min | Max | Unit | Description |

|--------|--------------------|--------------------------------|-----|-----|------|-------------|

|        | T <sub>css</sub>   | Chip select setup time (write) | 15  |     | ns   |             |

|        | Тсѕн               | Chip select hold time (write)  | 15  |     | ns   |             |

| CSX    | T <sub>CSS</sub>   | Chip select setup time (read)  | 60  |     | ns   |             |

|        | T <sub>scc</sub>   | Chip select hold time (read)   | 60  |     | ns   |             |

|        | T <sub>CHW</sub>   | Chip select "H" pulse width    | 40  |     | ns   |             |

|        | T <sub>SCYCW</sub> | Serial clock cycle (Write)     | 66  |     | ns   |             |

|        | T <sub>SHW</sub>   | SCL "H" pulse width (Write)    | 15  |     | ns   |             |

| SCL    | T <sub>SLW</sub>   | SCL "L" pulse width (Write)    | 15  |     | ns   |             |

| SUL    | T <sub>SCYCR</sub> | Serial clock cycle (Read)      | 150 |     | ns   |             |

|        | T <sub>SHR</sub>   | SCL "H" pulse width (Read)     | 60  |     | ns   |             |

|        | T <sub>SLR</sub>   | SCL "L" pulse width (Read)     | 60  |     | ns   |             |

| SDA    | T <sub>SDS</sub>   | Data setup time                | 10  |     | ns   |             |

| (DIN)  | T <sub>SDH</sub>   | Data hold time                 | 10  |     | ns   |             |

Table 4 3-line serial Interface Characteristics

Note: The rising time and falling time (Tr, Tf) of input signal are specified at 15 ns or less. Logic high and low levels are specified as 30% and 70% of VDDI for Input signals.

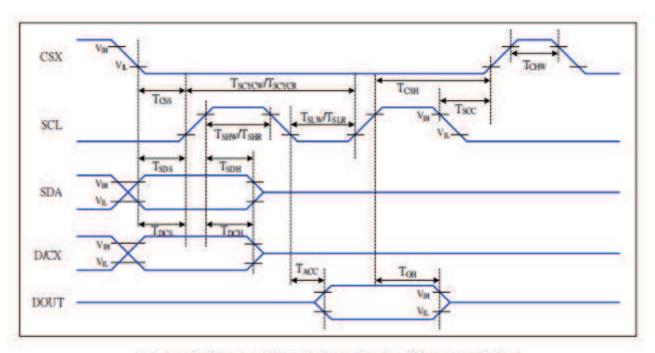

## 8.2 Serial Interface Characteristics (4-line serial):

Figure 2 4-line serial Interface Timing Characteristics

VDD =1.8, VDD=2.8, AGND=DGND=0V, Ta=25 ℃

| Signal           | Symbol           | Parameter                      | MIN | MAX   | Unit | Description           |

|------------------|------------------|--------------------------------|-----|-------|------|-----------------------|

|                  | Toss             | Chip select setup time (write) | 15  |       | ns   |                       |

|                  | Тсян             | Chip select hold time (write)  | 15  | - 13  | ns   |                       |

| CSX              | T <sub>CSS</sub> | Chip select setup time (read)  | 60  |       | ns   |                       |

|                  | Tscc             | Chip select hold time (read)   | 65  |       | ns   |                       |

|                  | T <sub>CHW</sub> | Chip select "H" pulse width    | 40  |       | ns   |                       |

|                  | Tscvcw           | Serial clock cycle (Write)     | 66  |       | ns   |                       |

| T <sub>SHW</sub> | T <sub>SHW</sub> | SCL "H" pulse width (Write)    | 15  |       | ns   | -write command & data |

|                  | T <sub>SUW</sub> | SCL "L" pulse width (Write)    | 15  |       | ns   | ram                   |

| SCL              | TSCYCR           | Serial clock cycle (Read)      | 150 |       | ns   |                       |

|                  | T <sub>SHR</sub> | SCL "H" pulse width (Read)     | 60  | 3. 13 | ns   | -read command & data  |

|                  | T <sub>SLR</sub> | SCL "L" pulse width (Read)     | 60  |       | ns   | ram                   |

| D/CX             | Toos             | D/CX setup time                | 10  |       | ns   |                       |

| DICX             | Трон             | D/CX hold time                 | 10  |       | ns   |                       |

| SDA              | T <sub>SDS</sub> | Data setup time                | 10  |       | ns   |                       |

| (DIN)            | Тѕрн             | Data hold time                 | 10  |       | ns   |                       |

Table 5 4-line serial Interface Characteristics

Note: The rising time and falling time (Tr, Tf) of input signal are specified at 15 ns or less. Logic high and low levels are specified as 30% and 70% of VDDI for Input signals.

### 8.3 RGB Interface Characteristics:

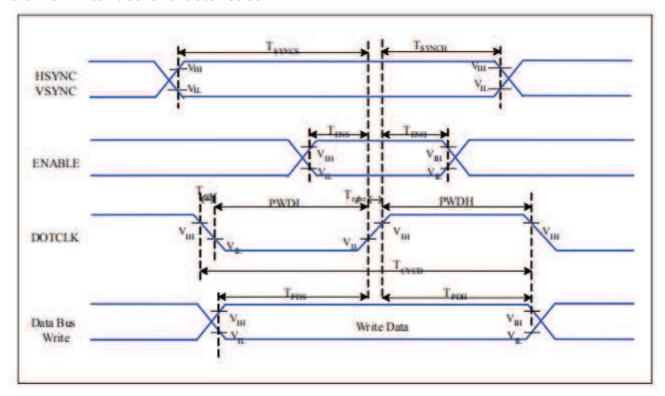

Figure 3 RGB Interface Timing Characteristics

VDDI=1.8, VDD=2.8, AGND=DGND=0V, Ta=25  $\,^{\circ}$ C

| Signal          | Symbol             | Parameter                     | MIN | MAX | Unit | Description |

|-----------------|--------------------|-------------------------------|-----|-----|------|-------------|

| HSYNC,<br>VSYNC | T <sub>SYNCS</sub> | VSYNC, HSYNC Setup Time       | 5   | -   | ns   |             |

| ENABLE          | T <sub>ENS</sub>   | Enable Setup Time             | 5   | -   | ns   |             |

| ENABLE          | T <sub>ENH</sub>   | Enable Hold Time              | 5   | -   | ns   |             |

|                 | PWDH               | DOTCLK High-level Pulse Width | 15  | -   | ns   |             |

| DOTOLK          | PWDL               | DOTCLK Low-level Pulse Width  | 15  | -   | ns   |             |

| DOTCLK          | T <sub>CYCD</sub>  | DOTCLK Cycle Time             | 33  | -   | ns   |             |

|                 | Trghr, Trghf       | DOTCLK Rise/Fall time         | -   | 15  | ns   |             |

|                 | T <sub>PDS</sub>   | PD Data Setup Time            | 5   | -   | ns   |             |

| DB              | T <sub>PDH</sub>   | PD Data Hold Time             | 5   | -   | ns   |             |

Table 6 18/16 Bits RGB Interface Timing Characteristics

#### 8.4 MIPI Interface Characteristics:

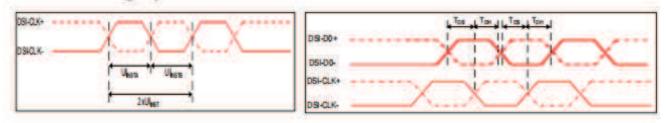

#### 8.4.1 High Speed Mode

Figure 4 DSI clock channel timing

Figure 5 Rising and falling time on clock and data channel

VDDI=1.8, VDD=2.8, AGND=DGND=0V, Ta=25 °C

| Signal     | Symbol                                     | Parameter                | MIN  | MAX  | Unit | Description                                       |

|------------|--------------------------------------------|--------------------------|------|------|------|---------------------------------------------------|

| DSI-CLK+/- | 2xUI <sub>INSTA</sub>                      | Double UI instantaneous  | 4    | 25   | ns   |                                                   |

| DSI-CLK+/- | Ul <sub>insta</sub><br>Ul <sub>instb</sub> | UI instantaneous halfs   | 2    | 12.5 | ns   | UI = UI <sub>INSTA</sub> =<br>UI <sub>INSTB</sub> |

| DSI-Dn+/-  | tDS                                        | Data to clock setup time | 0.15 | -    | UI   |                                                   |

| DSI-Dn+/-  | tDH                                        | Data to clock hold time  | 0.15 | -    | UI   |                                                   |

Table 7 Mipi Interface- High Speed Mode Timing Characteristics

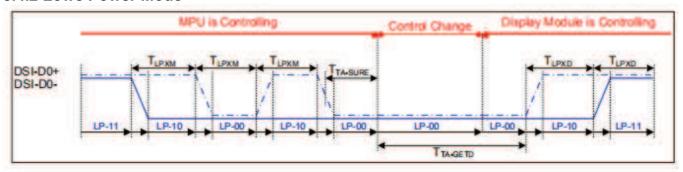

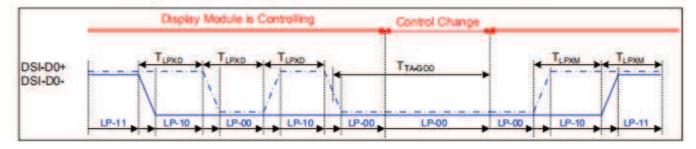

#### 8.4.2 Lowe Power Mode

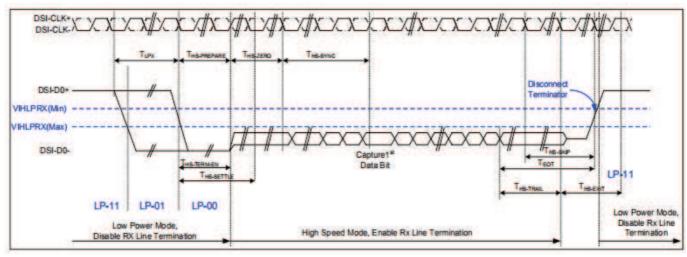

Figure 6 Bus Turnaround (BTA) from display module to MPU Timing

Figure 7 Bus Turnaround (BTA) from MPU to display module Timing

| Signal    | Symbol    | Parameter                 | MIN                 | MAX               | Unit | Description |  |

|-----------|-----------|---------------------------|---------------------|-------------------|------|-------------|--|

|           | TLPXM     | Length of LP-00,LP-01,    |                     | 75                | ns   |             |  |

| DSI-D0+/- |           | LP-10 or LP-11 periods    | 50                  |                   |      | Input       |  |

|           |           | MPU → Display Module      |                     |                   |      |             |  |

|           |           | Length of LP-00,LP-01,    |                     | 75                | ns   | Output      |  |

| DSI-D0+/- | TLPXD     | LP-10 or LP-11 periods    | 50                  |                   |      |             |  |

|           |           | MPU → Display Module      |                     |                   |      |             |  |

| DSI-D0+/- | TTA-SURED | Time-out before the MPU   | T <sub>LPXD</sub>   | 2xT <sub>LP</sub> | ns   | Output      |  |

| DSI-D0+/- |           | start driving             |                     | XD                |      |             |  |

| DSI-D0+/- | TTA-GETD  | Time to drive LP-00 by    | 5xT <sub>LPXD</sub> |                   | ns   | Input       |  |

| DSI-D0+/- |           | display module            |                     |                   |      |             |  |

| DSI-D0+/- | TT4 000   | Time to drive LP-00 after | 4xT <sub>LPXD</sub> |                   |      | Output      |  |

| D3I-D07/- | TTA-GOD   | turnaround request-MPU    |                     |                   | ns   | Output      |  |

Table 8 Mipi Interface Low Power Mode Timing Characteristics

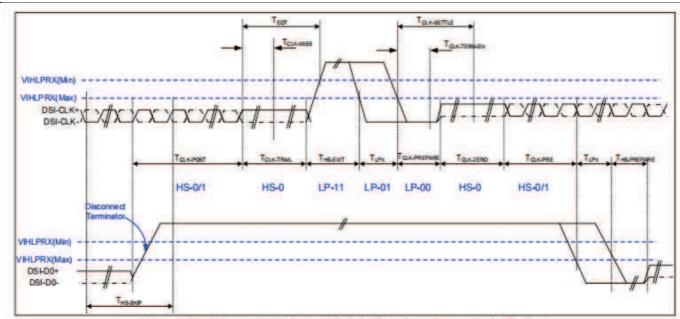

#### 8.4.3 DSI Bursts Mode

Figure 7 Data lanes-Low Power Mode to/from High Speed Mode Timing

Figure 8 Clock lanes- High Speed Mode to/from Low Power Mode Timing

VDD I=1.8,VDD=2.8, AGND=DGND=0 \( \)\Ta=25 \( \)\

| Signal     | Symbol                      | Parameter                                                                                                                     | MIN          | MAX          | Unit | Description |

|------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|------|-------------|

|            | **                          | Low Power Mode to High Speed Mo                                                                                               | ode Timi     | ng           |      | 01          |

| DSI-Dn+/-  | TLPX                        | Length of any low power state period                                                                                          | 50           | - 12         | ns   | Input       |

| DSI-Dn+/-  | THS-PREPARE                 | Time to drive LP-00 to prepare for HS transmission                                                                            | 40+4<br>UI   | 85+6<br>UI   | ns   | Input       |

| DSI-Dn+/-  | THS-TERM-EN                 | Time to enable data receiver<br>line termination measured from<br>when Dri crosses VILMAX                                     |              | 35+4<br>UI   | ns   | Input       |

| DSI-Dn+/-  | THS-PREPARE<br>+ THS-ZERO   | THS-PREPARE + time to drive<br>HS-0 before the sync sequence                                                                  | 140+<br>10UI |              | ns   | Input       |

|            | 72                          | High Speed Mode to Low Power Mo                                                                                               | ode Timi     | ng           |      |             |

| DSI-Dn+/-  | THS-SKIP                    | Time-out at display module to ignore transition period of EoT                                                                 | 40           | 55+4<br>UI   | ns   | Input       |

| DSI-Dn+/-  | THS-EXIT                    | Time to drive LP-11 after HS<br>burst                                                                                         | 100          |              | ns   | Input       |

| DSI-Dn+/-  | THS-TRAIL                   | Time to drive flipped differential<br>state after last payload data bit<br>of a HS transmission burst                         | 60+4<br>UI   | 7,637        | ns   | Input       |

|            | Hig                         | gh Speed Mode to/from Low Power                                                                                               | Mode Ti      | iming        |      | 74          |

| DSI-CLK+/- | TCLK-POS                    | Time that the MPU shall<br>continue sending HS clock after<br>the last associated data lane<br>has transition to LP mode      | 60+5<br>2UI  |              | ns   | Input       |

| DSI-CLK+/- | TCLK-TRAIL                  | Time to drive HS differential<br>state after last payload clock bit<br>of a HS transmission burst                             | 60           | 7/83         | ns   | Input       |

| DSI-CLK+/- | THS-EXIT                    | Time to drive LP-11 after HS<br>burst                                                                                         | 100          | 21           | ns   | Input       |

| DSI-CLK+/- | TCLK-PREPARE                | Time to drive LP-00 to prepare<br>for HS transmission                                                                         | 38           | 95           | ns   | Input       |

| DSI-CLK+/- | TCLK-TERM-EN                | Time-out at clock lan display<br>module to enable HS<br>transmission                                                          | 70           | 38           | ns   | Input       |

| DSI-CLK+/- | TCLK-PREPARE<br>+ TCLK-ZERO | Minimum lead HS-0 drive<br>period before starting clock                                                                       | 300          | *:           | ns   | Input       |

| DSI-CLK+/- | TCLK-PRE                    | Time that the HS clock shall be<br>driven prior to any associated<br>data lane beginning the<br>transition from LP to HS mode | BUI          |              | ns   | Input       |

| DSI-CLK+/- | теот                        | Time form start of TCLK-TRAIL period to start of LP-11 state                                                                  | *            | 105n<br>s+12 | ns   | Input       |

|            |                             |                                                                                                                               |              | UI           |      |             |

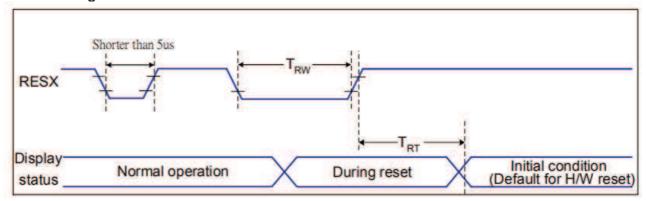

#### 8.5 Reset Timing

VDDI=1.8,VDD=2.8, AGND=DGND=0V, Ta=25 ℃

| Related Pins | Symbol | Parameter            | MIN               | MAX           | Unit |

|--------------|--------|----------------------|-------------------|---------------|------|

|              | TRW    | Reset pulse duration | 10                |               | us   |

| RESX         | TOT    | Deept consel         | ā                 | 5 (Note 1, 5) | ms   |

|              | TRT    | Reset cancel         | 120(Note 1, 6, 7) |               | ms   |

**Table 9 Reset Timing**

#### Notes:

- The reset cancel includes also required time for loading ID bytes, VCOM setting and other settings from NVM (or similar device) to registers. This loading is done every time when there is HW reset cancel time (tRT) within 5 ms after a rising edge of RESX.

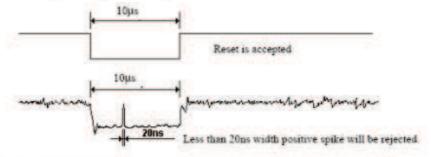

- 2. Spike due to an electrostatic discharge on RESX line does not cause irregular system reset according to the table below:

| RESX Pulse          | Action         |  |  |

|---------------------|----------------|--|--|

| Shorter than 5us    | Reset Rejected |  |  |

| Longer than 9us     | Reset          |  |  |

| Between 5us and 9us | Reset starts   |  |  |

- 3. During the Resetting period, the display will be blanked (The display is entering blanking sequence, which maximum time is 120 ms, when Reset Starts in Sieep Out –mode. The display remains the blank state in Sieep In –mode.) and then return to Default condition for Hardware Reset.

- 4. Spike Rejection also applies during a valid reset pulse as shown below:

- 5. When Reset applied during Sleep In Mode.

- 6. When Reset applied during Sleep Out Mode.

- It is necessary to wait 5-msec after releasing RESX before sending commands. Also Sleep Out command cannot be sent for 120msec.

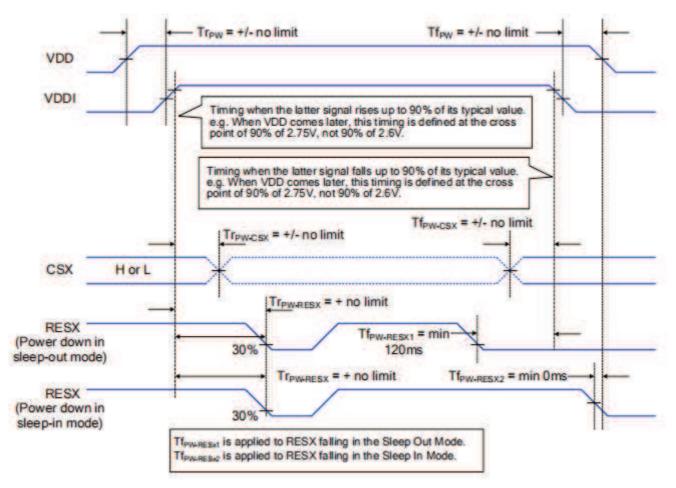

### 9. POWER SEQUENCE

VDDI and VDDA can be applied or powered down in any order. During the Power Off sequence, if the LCD is in the Sleep Out mode, VDDA and VDDI must be powered down with minimum 120msec. If the LCD is in the Sleep In mode, VDDA and VDDI can be powered down with minimum 0msec after the RESX is released. CSX can be applied at any timing or can be permanently grounded. RESX has high priority over CSX. Notes:

- 1. There will be no damage to the ST7701S if the power sequences are not met.

- 2. There will be no abnormal visible effects on the display panel during the Power On/Off Sequences.

- 3. There will be no abnormal visible effects on the display between the end of Power On Sequence and before receiving the Sleep Out command, and also between receiving the Sleep In command and the Power Off Sequence.

- 4. If the RESX line is not steadily held by the host during the Power On Sequence as defined in Sections 9.1 and

- 9.2, then it will be necessary to apply the Hardware Reset (RESX) after the completion of the Host Power On Sequence to ensure correct operations. Otherwise, all the functions are not guaranteed.

#### 9.1 Uncontrolled Power Off

The uncontrolled power-off means a situation which removed a battery without the controlled power off sequence. It will neither damage the module or the host interface.

If uncontrolled power-off happened, the display will go blank and there will not any visible effect on the display (blank display) and remains blank until "Power On Sequence" powers it up.

## 10. RELIABILITY TEST CONDITIONS

| No.  | Test item                           | Test condition                                                 |                 | Inspection after test                                                |

|------|-------------------------------------|----------------------------------------------------------------|-----------------|----------------------------------------------------------------------|

| 11.1 | High temperature storage test       | +80°C/240 hours                                                |                 |                                                                      |

| 11.2 | Low temperature storage test        | -30°C/240 hours                                                |                 |                                                                      |

| 11.3 | High temperature operating test     | +70°C/120 hours                                                |                 |                                                                      |

| 11.4 | Low temperature operating test      | g test -20°C/120 hours                                         |                 | Inspection after                                                     |

| 11.5 | Temperature cycle storage test      | -30°C ~ 25°C ~ +80°<br>(30min.) (10min.) (30                   | •               | 2~4hours storage at room temperature, the                            |

| 11.6 | High temperature high humidity test | +50°C*90% RH/120 hours                                         |                 | sample shall be free<br>from defects :<br>1.Current changing         |

| 11.7 | Vibration test                      | Amplitude : 1 inch Time: 45min                                 |                 | value before test and after test is 50% larger; 2. Function defect : |

|      |                                     | Drop direction:<br>1 corner/3 edges/6 sides 10 time            |                 | Non-display,abnormal-d isplay,missing lines, Short lines,ITO         |

|      |                                     | Packing weight(kg)                                             | Drop height(cm) | corrosion;                                                           |

| 11.8 | Drop test                           | <11                                                            | 80±1.6          | 3.Visual defect : Air bubble in the LCD,Seal                         |

|      |                                     | 11 ≦ G<21                                                      | 60±1.2          | leak,Glass crack.                                                    |

|      |                                     | 21 ≦ G<31                                                      | 50±1.0          |                                                                      |

|      |                                     | 31 ≦ G<40                                                      | 40±0.8          |                                                                      |

| 11.9 | ESD test                            | Air discharge: ±8KV, 10time<br>Contact discharge: ±4KV, 10time |                 |                                                                      |

#### Remark:

- 1. The test samples should be applied to only one test item.

- 2. Sample size for each test item is 3~5pcs.

- 3. For High temperature high humidity test, Pure water(Resistance>10 $M\Omega$ ) should be used.

- 4.In case of malfunction defect caused by ESD damage, if it would be recovered to normal state after resetting, it would be judged as a good part.

- 5.B/L evaluation should be excepted from reliability test with humidity and temperature: Some defects such as black spot/blemish can happen by natural chemical reaction with humidity and Fluorescence B/L has.

- 6.Failure judgment criterion: Basic specification, Electrical characteristic, Mechanical characteristic, Optical characteristic.

#### 11.INSPECTION CRITERION

Refer to 《Inspection Criterion for TFT Products-To customer》 V2.3, DOCUMENT NO.: GTK (WI) -00-QA-007

#### 12. HANDLING PRECAUTIONS

#### 12.1 Mounting method

The LCD module consists of two thin glass plates with polarizes which easily be damaged. And since the module in so constructed as to be fixed by utilizing fitting holes in the printed circuit board.

Extreme care should be needed when handling the LCD modules.

#### 12.2 Caution of LCD handling and cleaning

When cleaning the display surface, Use soft cloth with solvent

[recommended below] and wipe lightly:

- .lsopropyl alcohol

- Ethyl alcohol

Do not wipe the display surface with dry or hard materials that will damage the polarizer surface.

Do not use the following solvent :

- .Water

- Aromatics

Do not wipe ITO pad area with the dry or hard materials that will damage the ITO patterns

Do not use the following solvent on the pad or prevent it from being contaminated:

- Soldering flux

- •.Chlorine (Cl), Sulfur (S)

If goods were sent without being silicon coated on the pad, ITO patterns could be damaged due to the corrosion as time goes on.

If ITO corrosion happen by miss-handling or using some materials such as Chlorine (CI), Sulfur (S) from customer, Responsibility is on customer.

#### 12.3 Caution against static charge

The LCD module use C-MOS LSI drivers, so we recommended that you:

Connect any unused input terminal to Vdd or Vss, do not input any signals before power is turned on, and ground your body, work/assembly areas, assembly equipment to protect against static electricity.

#### 12.4 Packing

Module employ LCD elements and must be treated as such.

- Avoid intense shock and falls from a height.

- •. To prevent modules from degradation, do not operate or store them exposed direct to sunshine or high temperature/humidity.

#### 12.5 Caution for operation

- •.It is an indispensable condition to drive LCD's within the specified voltage limit since the higher voltage then the limit cause the shorter LCD life.

- •.An electrochemical reaction due to direct current causes LCD's undesirable deterioration, so that the use of direct current drive should be avoided.

- •.Response time will be extremely delayed at lower temperature then the operating temperature range and on the other hand at higher temperature LCD's how dark color in them. However those phenomena do not mean malfunction or out of order with LCD's, which will come back in the specified operation temperature.

- •.If the display area is pushed hard during operation, some font will be abnormally displayed but it resumes normal condition after turning off once.

- A slight dew depositing on terminals is a cause for electro-chemical reaction resulting in terminal open circuit.

- Usage under the maximum operating temperature, 50%Rh or less is required.

- •. When fixed patterns are displayed for a long time, remnant image is likely to occur.

### 12.6 Storage

In the case of storing for a long period of time for instance, for years for the purpose or replacement use, the following ways are recommended.

- Storing in an ambient temperature 10°C to 30°C, and in a relative humidity of 45% to 75%. Don't expose to sunlight or fluorescent light.

- •.Storing in a polyethylene bag with the opening sealed so as not to enter fresh air outside in it . And with no desiceant

- •.Placing in a dark place where neither exposure to direct sunlight nor light's keeping the storage temperature

range

• .Storing with no touch on polarizer surface by the anything else.

It is recommended to store them as they have been contained in the inner container at the time of delivery from us

#### 12.7 Safety

- •.It is recommendable to crash damaged or unnecessary LCD's into pieces and wash off liquid crystal by either of solvents such as acetone and ethanol, which should be burned up later.

- •. When any liquid leaked out of a damaged glass cell comes in contact with your hands, please wash it off well with soap and water.

#### 13. PRECAUTION FOR USE

- **13.1** A limit sample should be provided by the both parties on an occasion when the both parties agreed its necessity. Judgment by a limit sample shall take effect after the limit sample has been established and confirmed by the both parties.

- **13.2** On the following occasions, the handing of problem should be decided through discussion and agreement between responsible of the both parties.

- •. When a question is arisen in this specification.

- •. When a new problem is arisen which is not specified in this specifications.

- •. When an inspection specifications change or operating condition change in customer is reported to GTK, and some problem is arisen in this specification due to the change.

- •. When a new problem is arisen at the customer's operating set for sample evaluation in the customer site.

#### 14. PACKING SPECIFICATION

Please consult our technical department for detail information.

#### 15. INITIALIZATION CODE

```

/* Panel Name : HSD4.0IPS(HSD040BPN1-A00)

*/

/* Resulation : 480x480

/* Inversion : 2dot

/* Porch

: vbp=15, vfp=12

/* Line Time : 32us

/* Frame Rate : 60hz

WriteComm (0x11);

Delay ms(120);

WriteComm (0xFF);

WriteData (0x77);

WriteData (0x01);

WriteData (0x00);

WriteData (0x00);

WriteData (0x10);

WriteComm (0xC0);

WriteData (0x3B);

WriteData (0x00):

WriteComm (0xC1);

WriteData (0x0D);

WriteData (0x02);

WriteComm (0xC2);

WriteData (0x21);

WriteData (0x08);

WriteComm (0xB0);

WriteData (0x00);

WriteData (0x11);

WriteData (0x18);

WriteData (0x0E);

WriteData (0x11);

WriteData (0x06);

WriteData (0x07);

WriteData (0x08);

WriteData (0x07);

```

```

WriteData (0x22);

WriteData (0x04);

WriteData (0x12);

WriteData (0x0F);

WriteData (0xAA);

WriteData (0x31);

WriteData (0x18);

WriteComm (0xB1):

WriteData (0x00);

WriteData (0x11);

WriteData (0x19);

WriteData (0x0E);

WriteData (0x12);

WriteData (0x07);

WriteData (0x08);

WriteData (0x08);

WriteData (0x08);

WriteData (0x22):

WriteData (0x04);

WriteData (0x11);

WriteData (0x11);

WriteData (0xA9);

WriteData (0x32);

WriteData (0x18);

WriteComm (0xFF);

WriteData (0x77);

WriteData (0x01);

WriteData (0x00);

WriteData (0x00);

WriteData (0x11);

WriteComm (0xB0);

WriteData (0x60);

WriteComm (0xB1);

WriteData (0x30);

WriteComm (0xB2);

WriteData (0x87);

WriteComm (0xB3);

WriteData (0x80);

WriteComm (0xB5);

WriteData (0x49);

WriteComm (0xB7);

WriteData (0x85);

WriteComm (0xB8);

WriteData (0x21);

WriteComm (0xC1);

WriteData (0x78);

WriteComm (0xC2);

WriteData (0x78);

Delay_ms(20);

WriteComm (0xE0);

WriteData (0x00);

WriteData (0x1B);

WriteData (0x02);

WriteComm (0xE1);

WriteData (0x08);

WriteData (0xA0);

WriteData (0x00);

WriteData (0x00);

WriteData (0x07);

WriteData (0xA0);

```

```

WriteData (0x00);

WriteData (0x00);

WriteData (0x00);

WriteData (0x44);

WriteData (0x44);

WriteComm (0xE2);

WriteData (0x11);

WriteData (0x11):

WriteData (0x44);

WriteData (0x44);

WriteData (0xED);

WriteData (0xA0);

WriteData (0x00);

WriteData (0x00);

WriteData (0xEC);

WriteData (0xA0);

WriteData (0x00);

WriteData (0x00);

WriteComm (0xE3);

WriteData (0x00);

WriteData (0x00);

WriteData (0x11);

WriteData (0x11);

WriteComm (0xE4);

WriteData (0x44);

WriteData (0x44);

WriteComm (0xE5);

WriteData (0x0A);

WriteData (0xE9);

WriteData (0xD8);

WriteData (0xA0);

WriteData (0x0C);

WriteData (0xEB);

WriteData (0xD8);

WriteData (0xA0);

WriteData (0x0E);

WriteData (0xED);

WriteData (0xD8);

WriteData (0xA0);

WriteData (0x10);

WriteData (0xEF);

WriteData (0xD8);

WriteData (0xA0);

WriteComm (0xE6);

WriteData (0x00);

WriteData (0x00);

WriteData (0x11);

WriteData (0x11);

WriteComm (0xE7);

WriteData (0x44);

WriteData (0x44);

WriteComm (0xE8);

WriteData (0x09);

WriteData (0xE8);

WriteData (0xD8);

WriteData (0xA0);

WriteData (0x0B);

WriteData (0xEA);

WriteData (0xD8);

WriteData (0xA0);

```

WriteData (0x0D); WriteData (0xEC); WriteData (0xD8); WriteData (0xA0); WriteData (0x0F); WriteData (0xEE); WriteData (0xD8); WriteData (0xA0); WriteComm (0xEB); WriteData (0x02); WriteData (0x00); WriteData (0xE4); WriteData (0xE4); WriteData (0x88); WriteData (0x00); WriteData (0x40); WriteComm (0xEC); WriteData (0x3C); WriteData (0x00); WriteComm (0xED); WriteData (0xAB); WriteData (0x89); WriteData (0x76); WriteData (0x54); WriteData (0x02); WriteData (0xFF); WriteData (0xFF); WriteData (0xFF); WriteData (0xFF); WriteData (0xFF); WriteData (0xFF); WriteData (0x20); WriteData (0x45); WriteData (0x67); WriteData (0x98); WriteData (0xBA); WriteComm (0xFF); WriteData (0x77); WriteData (0x01); WriteData (0x00); WriteData (0x00); WriteData (0x00); WriteComm (0x29);